M2V64S30DTP-7

Overview

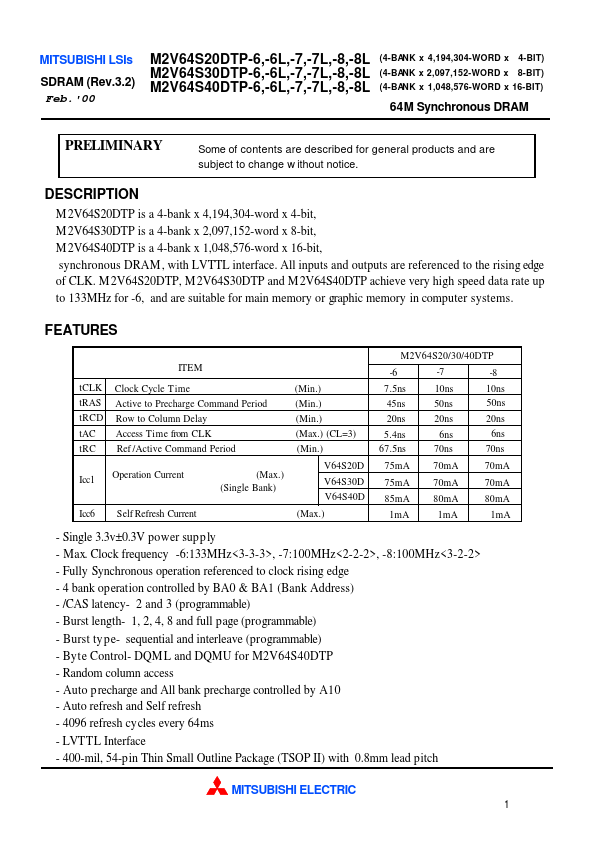

M 2V64S20DTP is a 4-bank x 4,194,304-word x 4-bit, M 2V64S30DTP is a 4-bank x 2,097,152-word x 8-bit, M 2V64S40DTP is a 4-bank x 1,048,576-word x 16-bit, synchronous DRAM , with LVTTL interface. All inputs and outputs are referenced to the rising edge of CLK.