M5M5Y5636TG-22

M5M5Y5636TG-22 is 18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM manufactured by Mitsubishi Electric.

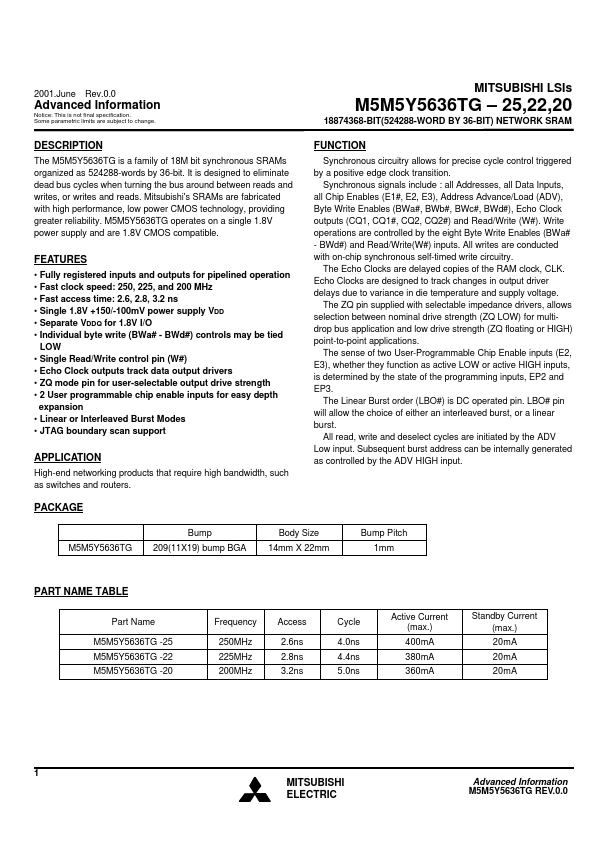

DESCRIPTION

The M5M5Y5636TG is a family of 18M bit synchronous SRAMs organized as 524288-words by 36-bit. It is designed to eliminate dead bus cycles when turning the bus around between reads and writes, or writes and reads. Mitsubishi's SRAMs are fabricated with high performance, low power CMOS technology, providing greater reliability. M5M5Y5636TG operates on a single 1.8V power supply and are 1.8V CMOS patible.

FUNCTION

Synchronous circuitry allows for precise cycle control triggered by a positive edge clock transition. Synchronous signals include : all Addresses, all Data Inputs, all Chip Enables (E1#, E2, E3), Address Advance/Load (ADV), Byte Write Enables (BWa#, BWb#, BWc#, BWd#), Echo Clock outputs (CQ1, CQ1#, CQ2, CQ2#) and Read/Write (W#). Write operations are controlled by the eight Byte Write Enables (BWa#

- BWd#) and Read/Write(W#) inputs. All writes are conducted with on-chip synchronous self-timed write circuitry. The Echo Clocks are delayed copies of the RAM clock, CLK. Echo Clocks are designed to track changes in output driver delays due to variance in die temperature and supply voltage. The ZQ pin supplied with selectable impedance drivers, allows selection between nominal drive strength (ZQ LOW) for multidrop bus application and low drive strength (ZQ floating or HIGH) point-to-point applications. The sense of two User-Programmable Chip Enable inputs (E2, E3), whether they function as active LOW or active HIGH inputs, is determined by the state of the programming inputs, EP2 and EP3. The Linear Burst order (LBO#) is DC operated pin. LBO# pin will allow the choice of either an interleaved burst, or a linear burst. All read, write and deselect cycles are initiated by the ADV Low input. Subsequent burst address can be internally generated as controlled by the ADV HIGH input.

FEATURES

- Fully registered inputs and outputs for pipelined operation

- Fast clock speed: 250, 225, and 200 MHz

- Fast access time: 2.6, 2.8, 3.2 ns

- Single 1.8V +150/-100m V...