MC100ES6130 Overview

Key Specifications

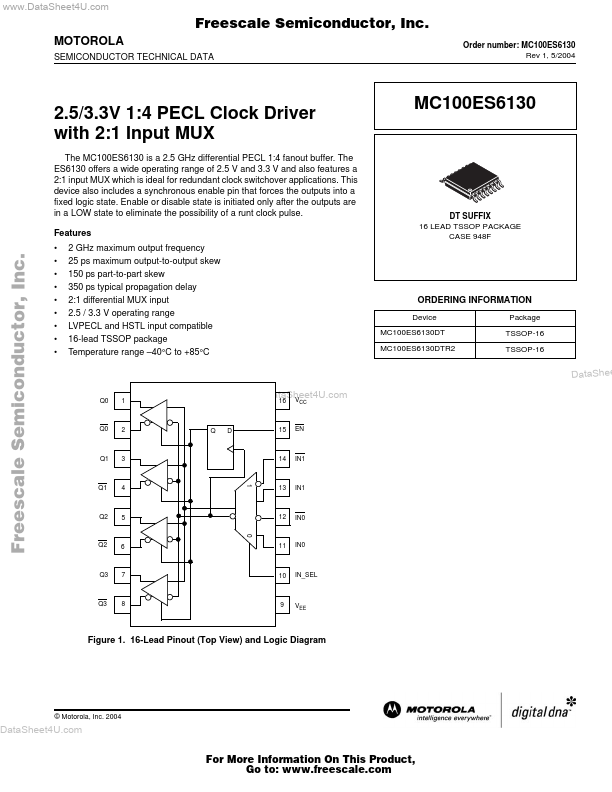

Package: TSSOP

Mount Type: Surface Mount

Pins: 16

Operating Voltage: 2.5 V

Key Features

- a 2:1 input MUX which is ideal for redundant clock switchover applications

- This device also includes a synchronous enable pin that forces the outputs into a fixed logic state

- Enable or disable state is initiated only after the outputs are in a LOW state to eliminate the possibility of a runt clock pulse

- Features MC100ES6130 DT SUFFIX 16 LEAD TSSOP PACKAGE CASE 948F Freescale Semiconductor, Inc