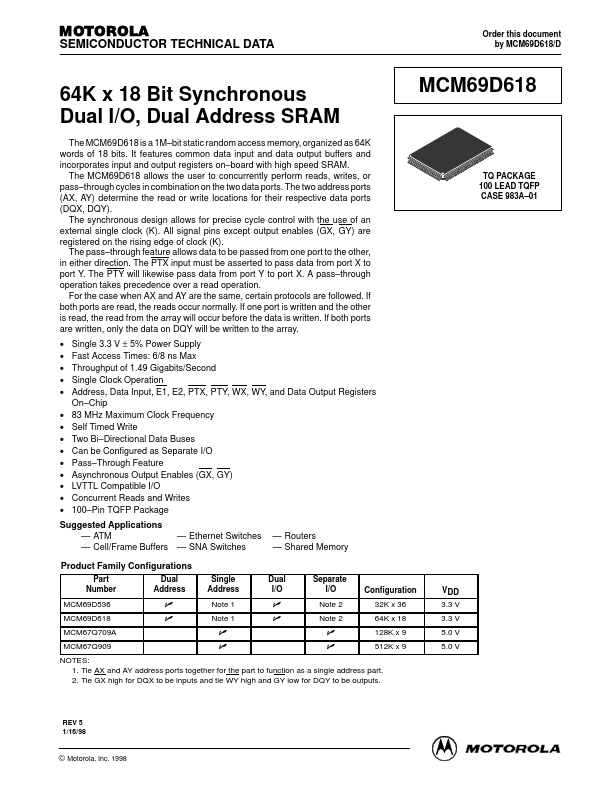

MCM69D618

Overview

- Single 3.3 V ± 5% Power Supply Fast Access Times: 6/8 ns Max Throughput of 1.49 Gigabits/Second Single Clock Operation Address, Data Input, E1, E2, PTX, PTY, WX, WY, and Data Output Registers On-Chip 83 MHz Maximum Clock Frequency Self Timed Write Two Bi-Directional Data Buses Can be Configured as Separate I/O Pass-Through Feature Asynchronous Output Enables (GX, GY) LVTTL Compatible I/O Concurrent Reads and Writes 100-Pin TQFP Package - Routers - Shared Memory