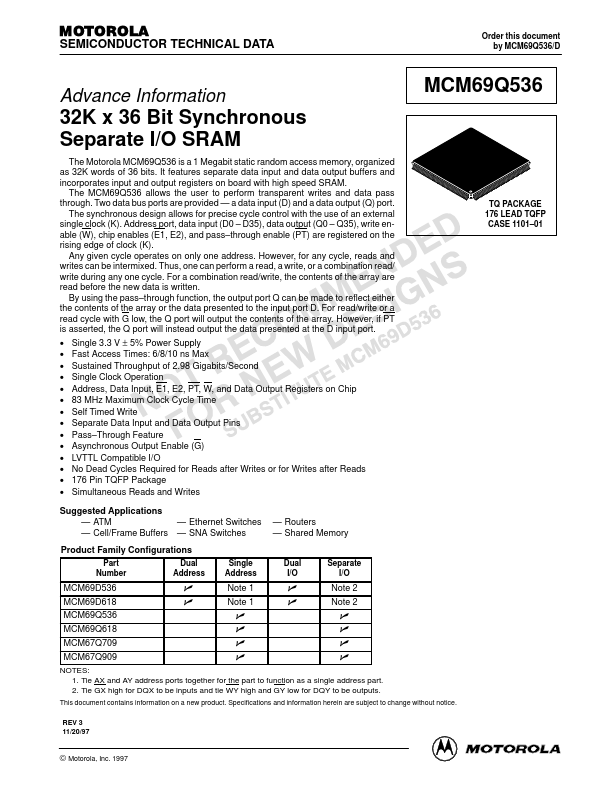

MCM69Q536 Overview

Key Features

- separate data input and data output buffers and incorporates input and output registers on board with high speed SRAM

- The MCM69Q536 allows the user to perform transparent writes and data pass through

- Two data bus ports are provided - a data input (D) and a data output (Q) port

- The synchronous design allows for precise cycle control with the use of an external single clock (K)

- Any given cycle operates on only one address