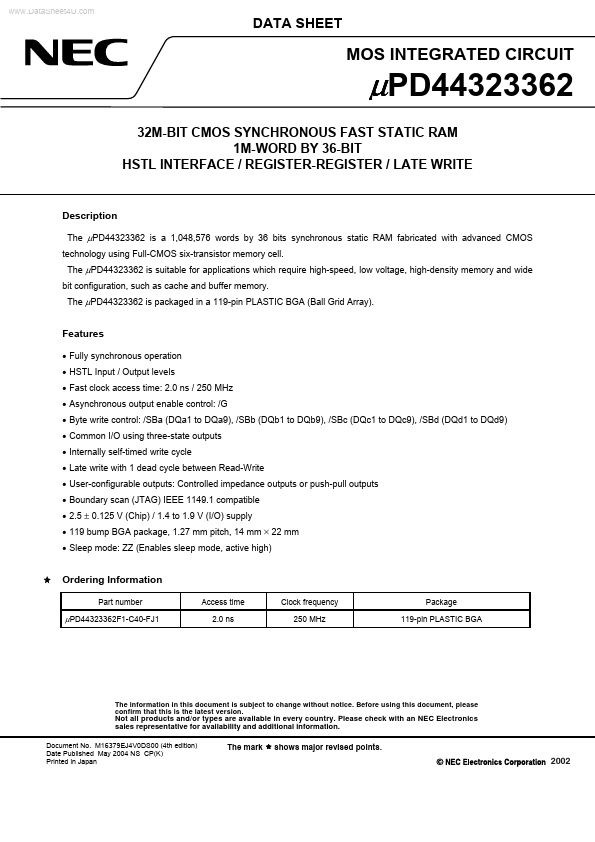

UPD44323362

Overview

The µPD44323362 is a 1,048,576 words by 36 bits synchronous static RAM fabricated with advanced CMOS technology using Full-CMOS six-transistor memory cell. The µPD44323362 is suitable for applications which require high-speed, low voltage, high-density memory and wide bit configuration, such as cache and buffer memory.

- Fully synchronous operation

- HSTL Input / Output levels

- Fast clock access time: 2.0 ns / 250 MHz

- Asynchronous output enable control: /G

- Byte write control: /SBa (DQa1 to DQa9), /SBb (DQb1 to DQb9), /SBc (DQc1 to DQc9), /SBd (DQd1 to DQd9)

- Common I/O using three-state outputs

- Internally self-timed write cycle

- Late write with 1 dead cycle between Read-Write

- User-configurable outputs: Controlled impedance outputs or push-pull outputs

- Boundary scan (JTAG) IEEE 1149.1 compatible