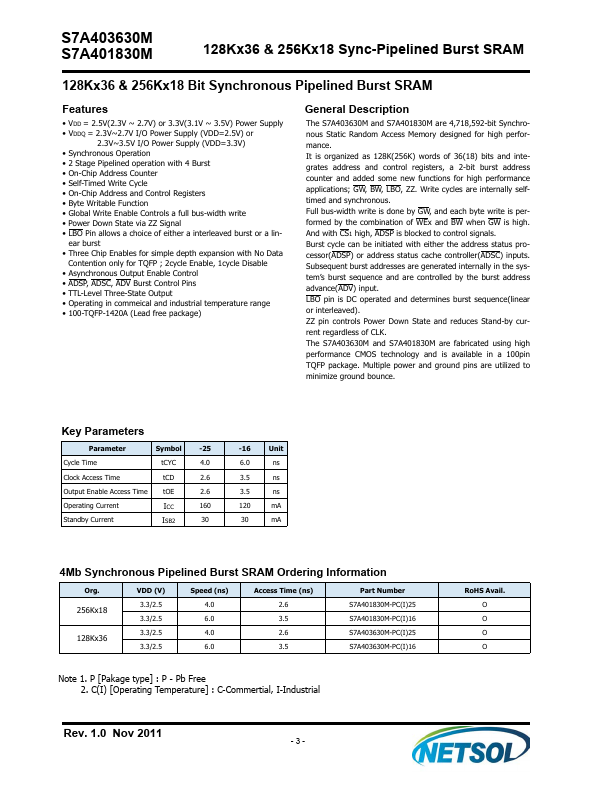

S7A403630M Description

The S7A403630M and S7A401830M are 4,718,592-bit Synchronous Static Random Access Memory designed for high performance. It is organized as 128K(256K) words of 36(18) bits and integrates address and control registers, a 2-bit burst address counter and added some new functions for high performance applications; Write cycles are internally selftimed and synchronous.

S7A403630M Key Features

- VDD = 2.5V(2.3V ~ 2.7V) or 3.3V(3.1V ~ 3.5V) Power Supply

- VDDQ = 2.3V~2.7V I/O Power Supply (VDD=2.5V) or

- Synchronous Operation

- 2 Stage Pipelined operation with 4 Burst

- On-Chip Address Counter

- Self-Timed Write Cycle

- On-Chip Address and Control Registers

- Byte Writable Function

- Global Write Enable Controls a full bus-width write

- Power Down State via ZZ Signal