74F109 Overview

Key Specifications

Package: SOP

Mount Type: Surface Mount

Pins: 16

Operating Voltage: 5 V

Description

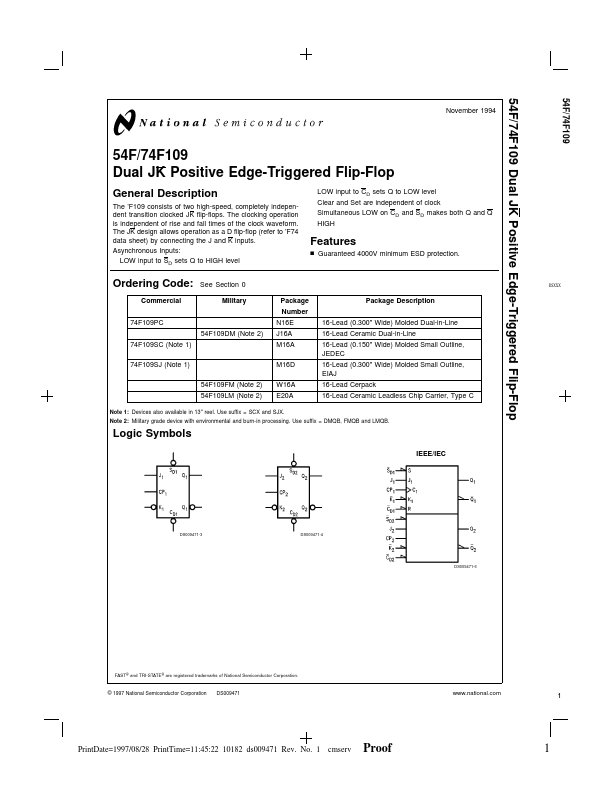

The ’F109 consists of two high-speed, completely independent transition clocked JK flip-flops. The clocking operation is independent of rise and fall times of the clock waveform.

Key Features

- 54F109DM (Note

- 74F109SJ (Note

- 54F109FM (Note

- 54F109LM (Note