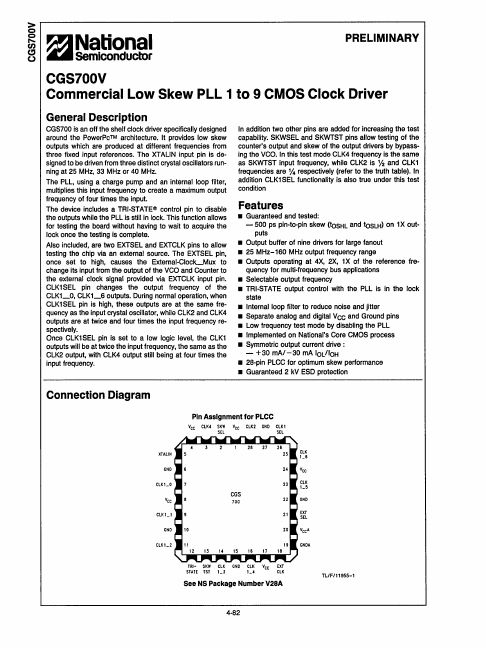

| Part | CGS700V |

|---|---|

| Description | Commercial Low Skew PLL 1 to 9 CMOS Clock Driver |

| Manufacturer | National Semiconductor |

| Size | 180.74 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| CGS703U050X5L | CDE | High-Cap Screw Terminal Aluminum Electrolytic Capacitor |

| CGS702U075R2L | CDE | High-Cap Screw Terminal Aluminum Electrolytic Capacitor |

| CGS702T400X5R | CDE | High-Cap Screw Terminal Aluminum Electrolytic Capacitor |

| CGS704U016X5L | CDE | High-Cap Screw Terminal Aluminum Electrolytic Capacitor |

| CGS703U025X4C | CDE | High-Cap Screw Terminal Aluminum Electrolytic Capacitor |