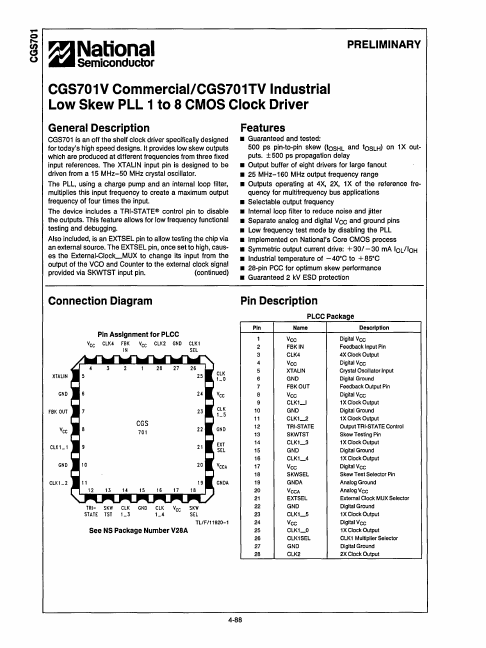

CGS701V

Description

CGS701 is an off the shelf clock driver specifically designed for today's high speed designs. It provides low skew outputs which are produced at different frequencies from three fixed input references.

Key Features

- Guaranteed and tested: 500 ps pin-to-pin skew (tOSHL and tOSLH) on 1X out- puts. ± 500 ps propagation delay

- Output buffer of eight drivers for large fanout

- 25 MHz-160 MHz output frequency range

- Outputs operating at 4X, 2X, 1X of the reference frequency for multifrequency bus applications

- Selectable output frequency

- Internal loop filter to reduce noise and jitter

- Separate analog and digital Vee and ground pins

- Low frequency test mode by disabling the PLL

- Implemented on National's Core CMOS process

- Symmetric output current drive: + 30/ - 30 mA IOLliOH