Overview

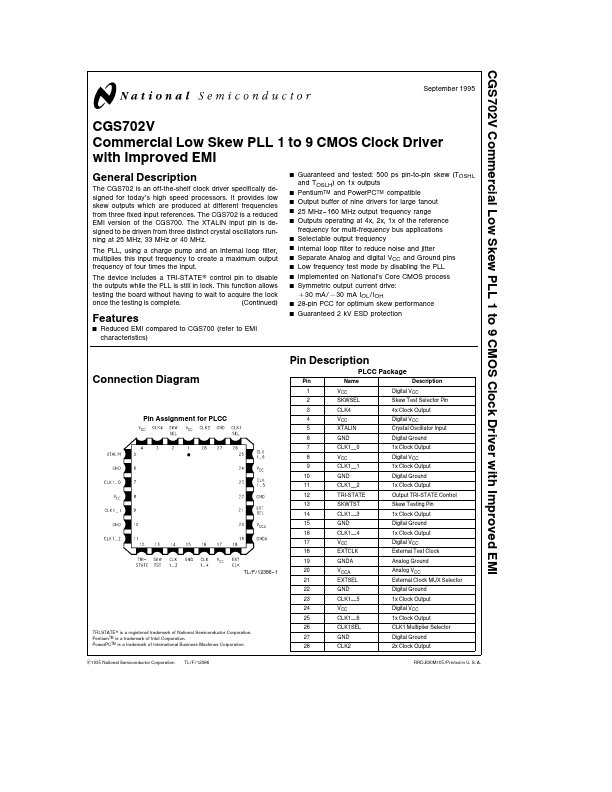

The CGS702 is an off-the-shelf clock driver specifically designed for today’s high speed processors It provides low skew outputs which are produced at different frequencies from three fixed input references The CGS702 is a reduced EMI version of the CGS700 The XTALIN input pin is designed to be driven from three distinct crystal oscillators running at 25 MHz 33 MHz or 40 MHz The PLL using a charge pump and an internal loop filter multiplies this input frequency to create a maximum output frequency of four times the input The device includes a TRI-STATE control pin to disable the outputs while the PLL is still in lock This function allows testing the board without having to wait to acquire the lock once the testing is complete (Continued) Y Y Y Y Y Y Y Y Y Y Y Y Y.