DS90CR283 Overview

Key Specifications

Package: TSSOP

Mount Type: Surface Mount

Pins: 56

Operating Voltage: 5 V

Description

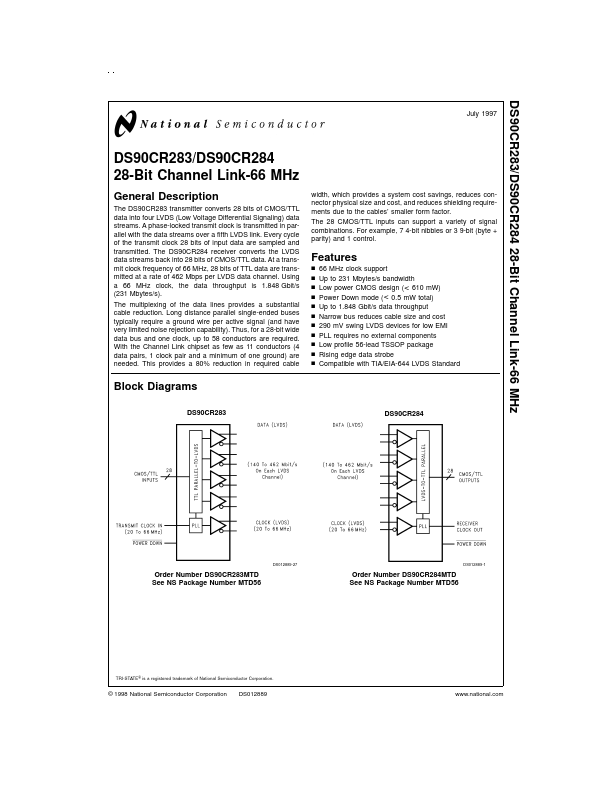

The DS90CR283 transmitter converts 28 bits of CMOS/TTL data into four LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fifth LVDS link.