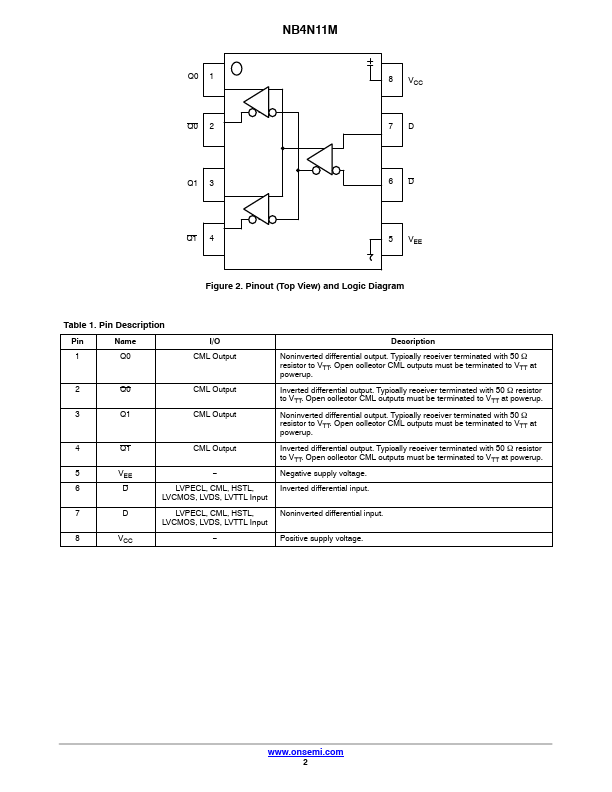

NB4N11M Overview

The NB4N11M is a differential 1−to−2 clock/data distribution/translation chip with CML output structure, targeted for high−speed clock/data applications. The device is functionally equivalent to the EP11, LVEP11, SG11 or 7L11M devices. Device produces two identical differential output copies of clock or data signal operating up to 2.5 GHz or 2.5 Gb/s, respectively.

NB4N11M Key Features

- Maximum Input Clock Frequency > 2.5 GHz

- Maximum Input Data Rate > 2.5 Gb/s

- Typically 1 ps of RMS Clock Jitter

- Typically 10 ps of Data Dependent Jitter @ 2.5 Gb/s, RL = 25 W

- 420 ps Typical Propagation Delay

- 150 ps Typical Rise and Fall Times

- Operating Range: VCC = 3.0 V to 3.6 V with VEE = 0 V and

- Functionally patible with Existing 2.5 V / 3.3 V LVEL, LVEP

- These Devices are Pb-Free, Halogen Free and are RoHS pliant

- For additional marking information, refer to Application Note AND8002/D