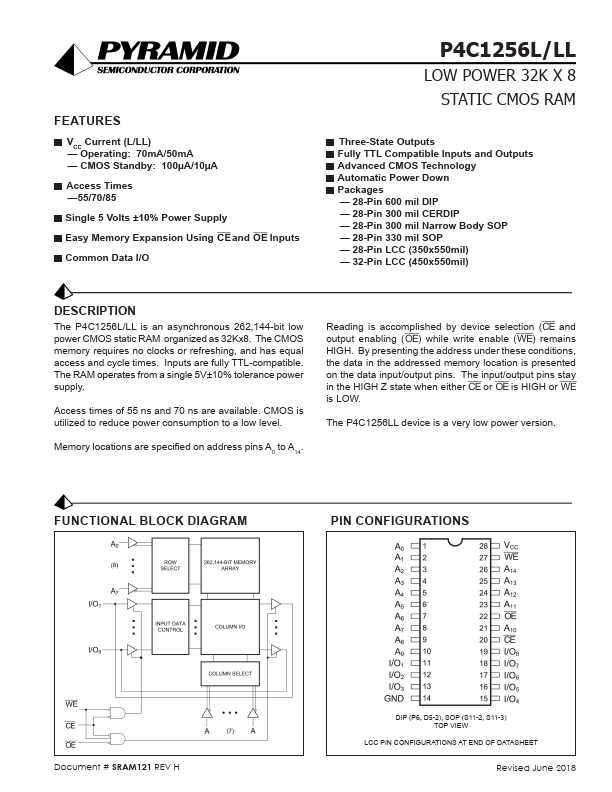

P4C1256L Description

The P4C1256L/LL is an asynchronous 262,144-bit low power CMOS static RAM organized as 32Kx8. The CMOS memory requires no clocks or refreshing, and has equal access and cycle times. Inputs are fully TTL-patible.

P4C1256L Key Features

- Operating: 70mA/50mA

- CMOS Standby: 100µA/10µA

- 28-Pin 600 mil DIP

- 28-Pin 300 mil CERDIP

- 28-Pin 300 mil Narrow Body SOP

- 28-Pin 330 mil SOP

- 28-Pin LCC (350x550mil)

- 32-Pin LCC (450x550mil)