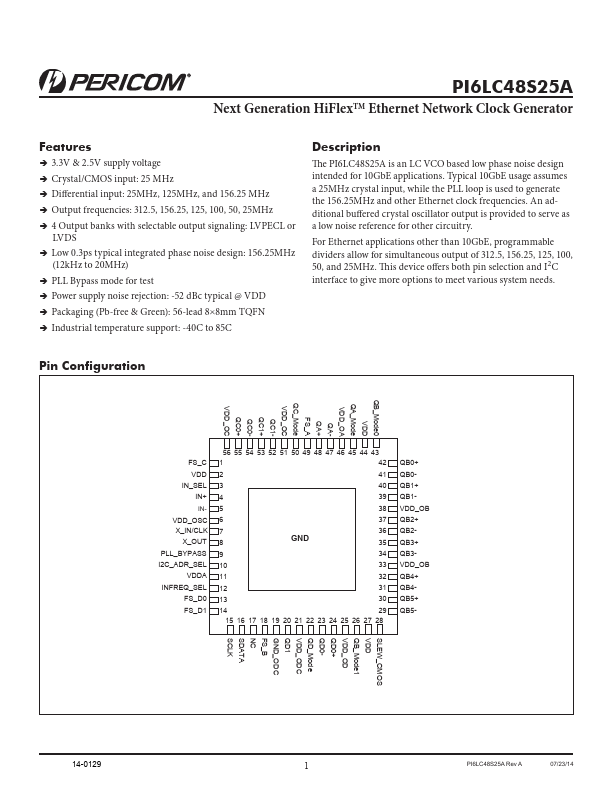

| Part | PI6LC48S25A |

|---|---|

| Description | Ethernet Network Clock Generator |

| Manufacturer | Pericom Semiconductor |

| Size | 665.90 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| XR2206 | Exar | Monolithic Function Generator |

| AN97 | Maxim Integrated | Telephone Tone Generator |

| AN97 | Maxim Integrated | Telephone Tone Generator Requires No trimming |