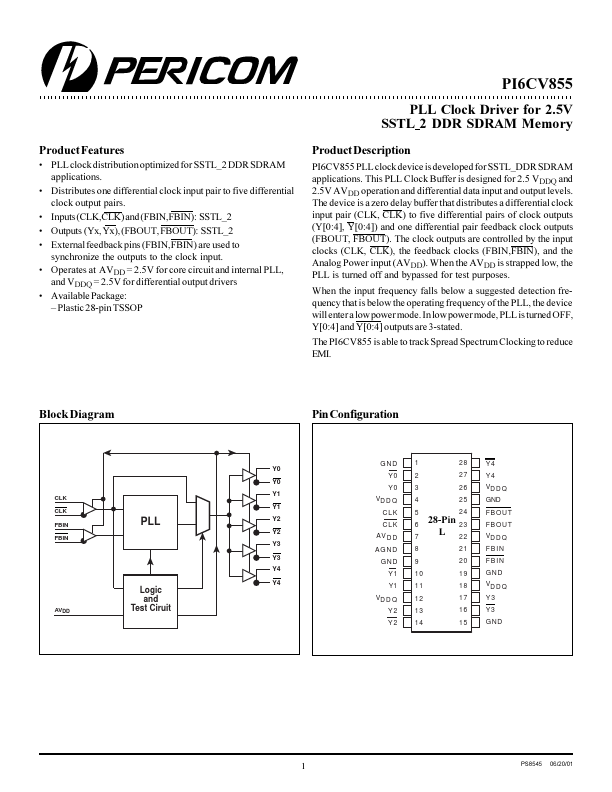

PI6CV855 Description

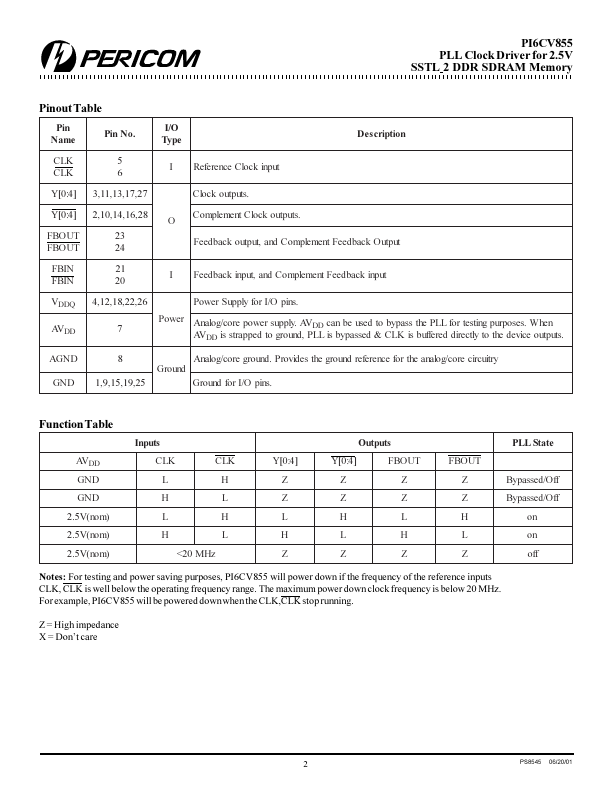

PI6CV855 PLL clock device is developed for SSTL_DDR SDRAM applications. This PLL Clock Buffer is designed for 2.5 VDDQ and 2.5V AVDD operation and differential data input and output levels. The device is a zero delay buffer that distributes a differential clock input pair (CLK, CLK) to five differential pairs of clock outputs (Y[0:4], Y[0:4]) and one differential pair feedback clock outputs (FBOUT, FBOUT).