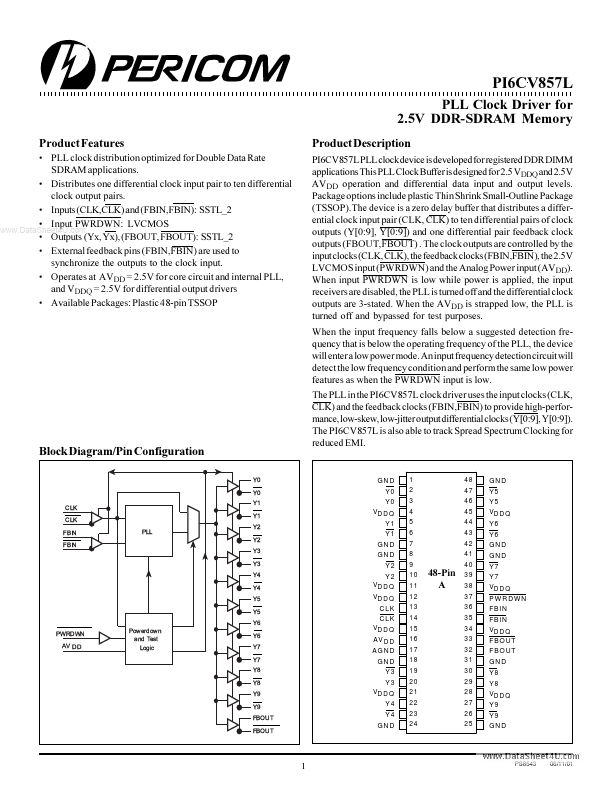

PI6CV857L Description

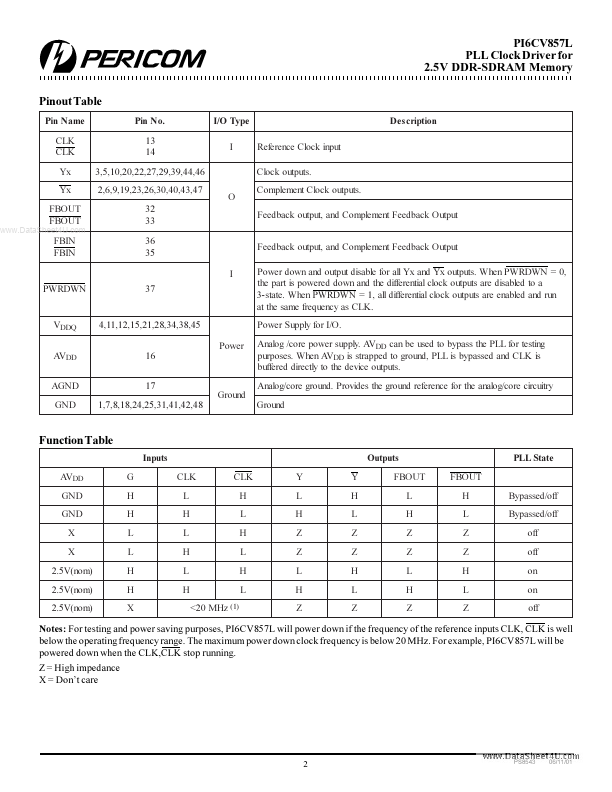

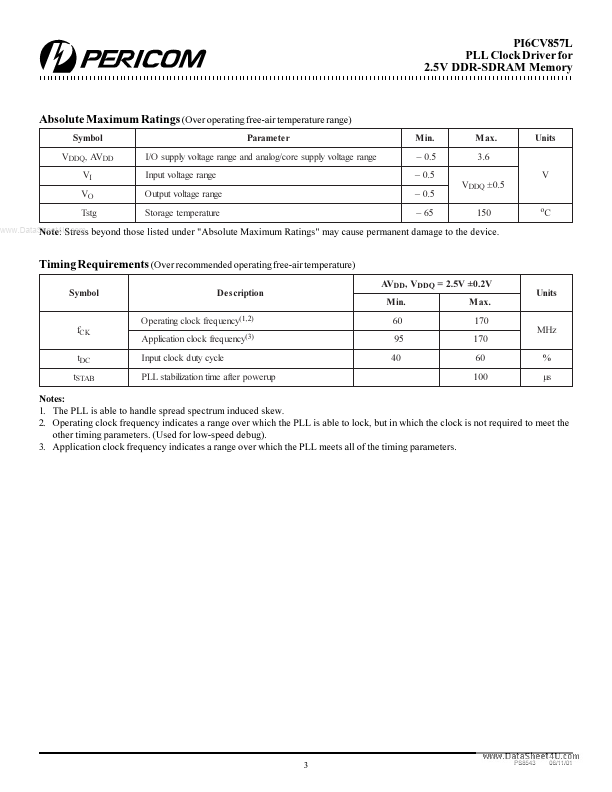

PI6CV857L PLL clock device is developed for registered DDR DIMM applications This PLL Clock Buffer is designed for 2.5 VDDQ and 2.5V AVDD operation and differential data input and output levels. Package options include plastic Thin Shrink Small-Outline Package (TSSOP).The device is a zero delay buffer that distributes a differential clock input pair (CLK, CLK) to ten differential pairs of clock outputs (Y[0:9],...