PLL601-12

PLL601-12 is Dual Output PLL Clock manufactured by PhaseLink.

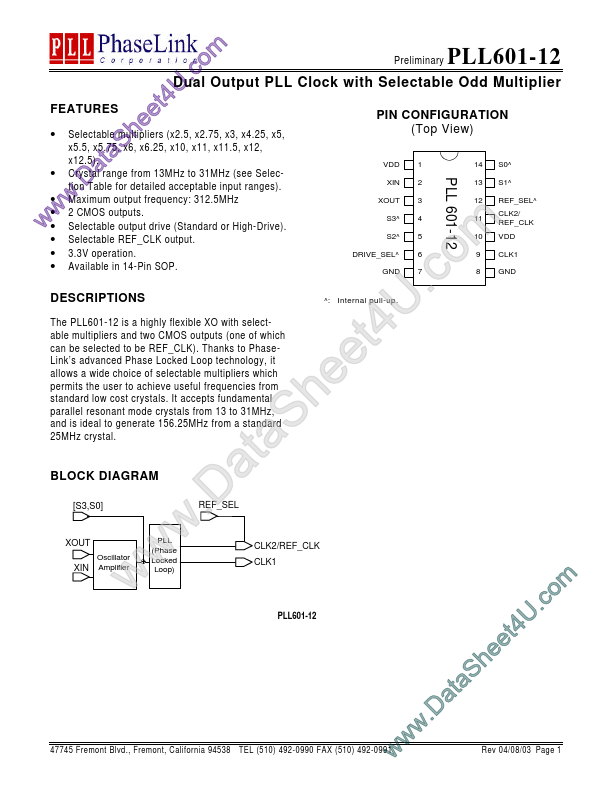

FEATURES e PIN CONFIGURATION e (Top View) h

- Selectable multipliers (x2.5, x2.75, x3, x4.25, x5, x5.5, x5.75, S x6, x6.25, x10, x11, x11.5, x12, a x12.5). t

- Crystala range from 13MHz to 31MHz (see Selec D tion Table for detailed acceptable input ranges). .

- w Maximum output frequency: 312.5MHz

- w 2 CMOS outputs. w- Selectable output drive (Standard or High-Drive).

VDD 1 2 3 4 5 6 7 14 13 12 11 10 9 8 S0^ S1^

PLL 601-12

XOUT S3^ S2^

REF_SEL^ CLK2/ REF_CLK VDD

- -

- Selectable REF_CLK output. 3.3V operation. Available in 14-Pin SOP.

DESCRIPTIONS

The PLL601-12 is a highly flexible XO with selectable multipliers and two CMOS outputs (one of which can be selected to be REF_CLK). Thanks to Phase Link’s advanced Phase Locked Loop technology, it allows a wide choice of selectable multipliers which permits the user to achieve useful frequencies from standard low cost crystals. It accepts fundamental parallel resonant mode crystals from 13 to 31MHz, and is ideal to generate 156.25MHz from a standard 25MHz crystal.

BLOCK DIAGRAM

[S3,S0]

XOUT

Oscillator XIN Amplifier m o .c U 4 t e e h S a t a .D w w w

DRIVE_SEL^ GND ^: Internal pull-up.

CLK1 GND

REF_SEL

PLL (Phase Locked Loop)

CLK2/REF_CLK CLK1

47745 Fremont Blvd., Fremont, California 94538 TEL (510) 492-0990 FAX (510) 492-0991 m o .c 4U t e e h S a t a D . w w w

Rev 04/08/03 Page 1

Preliminary

Dual Output PLL Clock with Selectable Odd Multiplier

FREQUENCY SELECTION TABLE

S3 0 0 0 0 0 0 0 0 1 1 1 1 1 S2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 S1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 S0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Xtal Max Xtal Min Reserved Reserved X 4.25 X 11 X 12 X 12.5 X 5.75 X3 X 11.5 X 5.5 X 2.75 X5 X 2.5 X 10 X6 X 6.25 Multiplier

1 1

36 28 26 25 27 26 27 28 28 31 31 31 26 25

19 15 14 13 14 14 14 15 15 16 16 16 14 13

Note: Internal pull-ups default S3, S2, S1, and S0 to ‘1’ when not connected

PIN DESCRIPTION

Name

XIN XOUT DRIVE_SEL GND CLK1 CLK2/REF_CLK REF_SEL S0 S1 S2 S3...