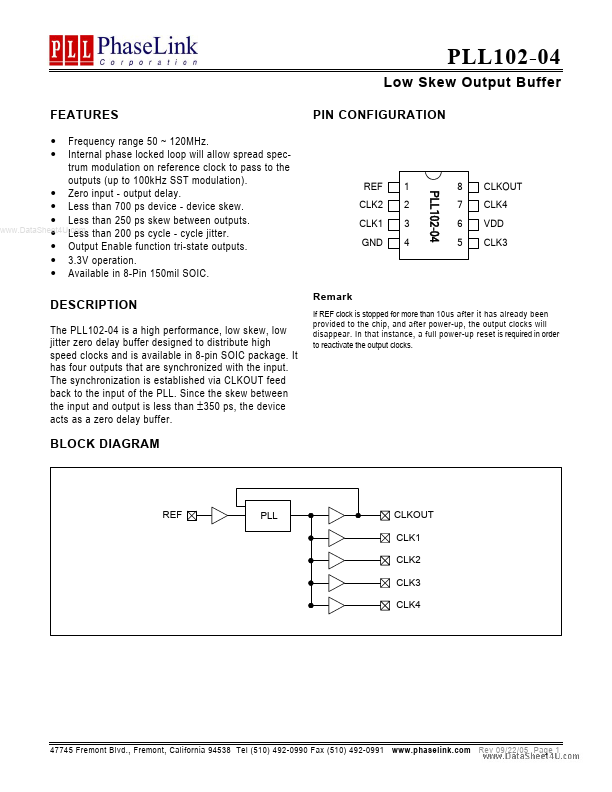

PLL102-04 Description

The PLL102-04 is a high performance, low skew, low jitter zero delay buffer designed to distribute high speed clocks and is available in 8-pin SOIC package. It has four outputs that are synchronized with the input. The synchronization is established via CLKOUT feed back to the input of the PLL.

PLL102-04 Key Features

- Zero input

- output delay

- Less than 700 ps device

- device skew

- Less than 250 ps skew between outputs

- Less than 200 ps cycle

- cycle jitter

- Output Enable function tri-state outputs

- 3.3V operation

- Available in 8-Pin 150mil SOIC