Datasheet Summary

Preliminary

Programmable DDR Zero Delay Clock Driver

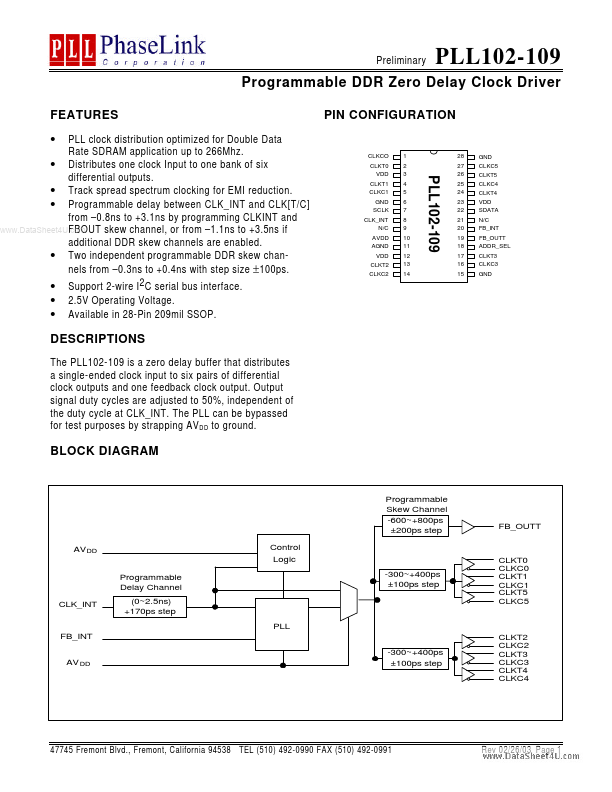

Features

PLL clock distribution optimized for Double Data Rate SDRAM application up to 266Mhz.

- Distributes one clock Input to one bank of six differential outputs.

- Track spread spectrum clocking for EMI reduction.

- Programmable delay between CLK_INT and CLK[T/C] from

- 0.8ns to +3.1ns by programming CLKINT and .. FBOUT skew channel, or from

- 1.1ns to +3.5ns if additional DDR skew channels are enabled.

- Two independent programmable DDR skew channels from

- 0.3ns to +0.4ns with step size ± 100ps.

- Support 2-wire I 2 C serial bus interface.

- - 2.5V Operating Voltage. Available in 28-Pin 209mil SSOP.

-...