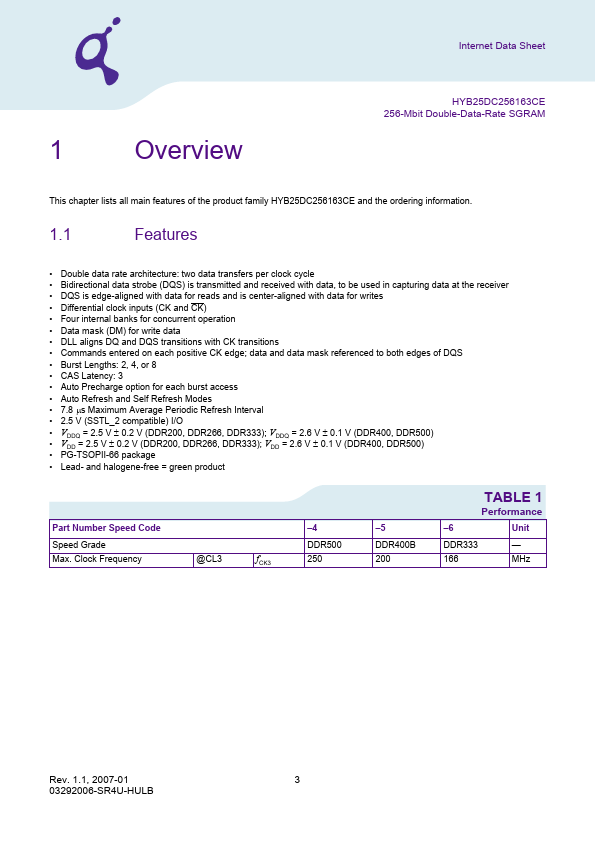

HYB25DC256163CE-6 Key Features

- Double data rate architecture: two data transfers per clock cycle

- Bidirectional data strobe (DQS) is transmitted and received with data, to be used in capturing data at the receiver

- DQS is edge-aligned with data for reads and is center-aligned with data for writes

- Differential clock inputs (CK and CK)

- Four internal banks for concurrent operation

- Data mask (DM) for write data

- DLL aligns DQ and DQS transitions with CK transitions

- mands entered on each positive CK edge; data and data mask referenced to both edges of DQS

- Burst Lengths: 2, 4, or 8

- CAS Latency: 3