Datasheet Summary

ICS95V1 5 7

2.5V Single-Ended to SSTL_2 Clock Driver (45MHz

- 233MHz)

Remended Application: Single-ended clock input with zero delay board fan out

Product Description/Features

:

- Low skew, low jitter PLL clock driver

- 1 to 10 differential clock distribution (SSTL_2)

- Feedback pin for input to output synchronization

- PD# for power management

- Spread Spectrum tolerant inputs

Switching Characteristics:

- CYCLE

- CYCLE jitter: <60ps

- OUTPUT

- OUTPUT skew: <60ps

- Period jitter: ±30ps

- DUTY CYCLE: 49.5%

- 50.5%

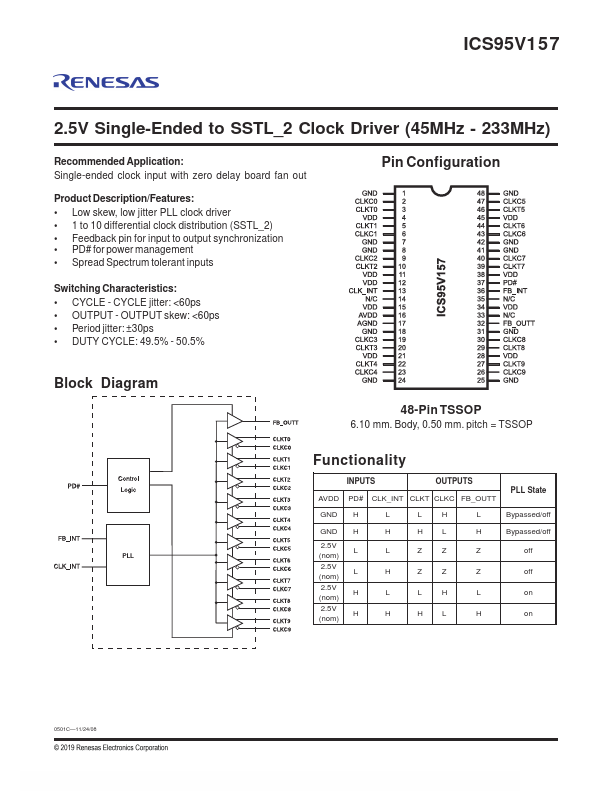

Pin Configuration

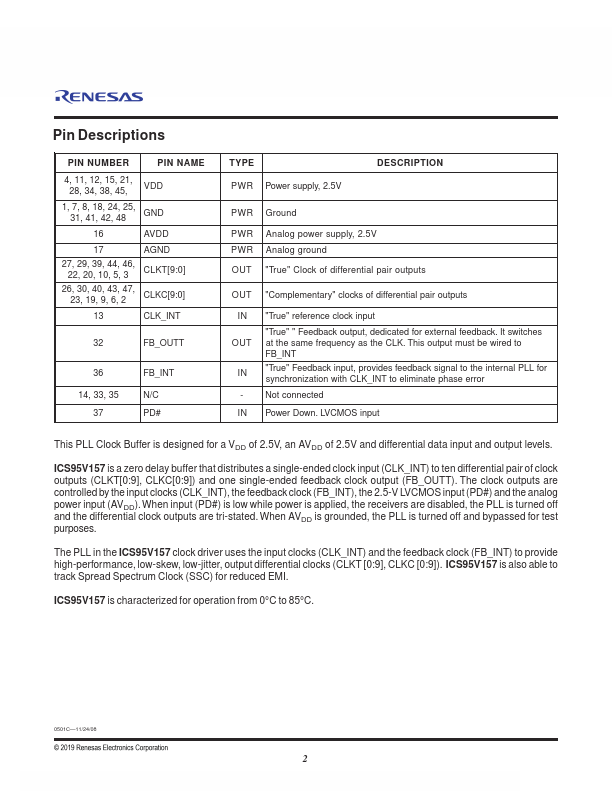

Block Diagram

48-Pin TSSOP

6.10 mm. Body, 0.50 mm. pitch = TSSOP

Functionality

INPUTS

OUTPUTS

AVDD PD# CLK_INT CLKT CLKC FB_OUTT

PLL State

GND...