KAD5512P Description

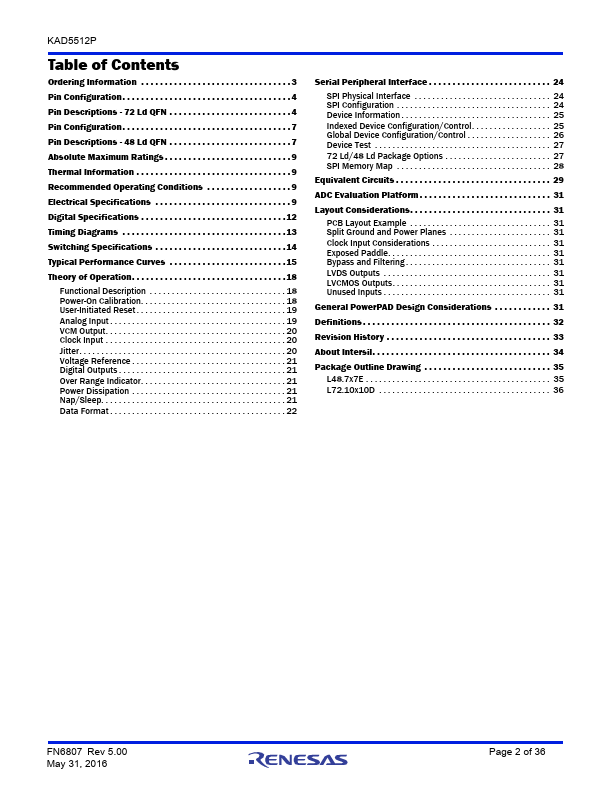

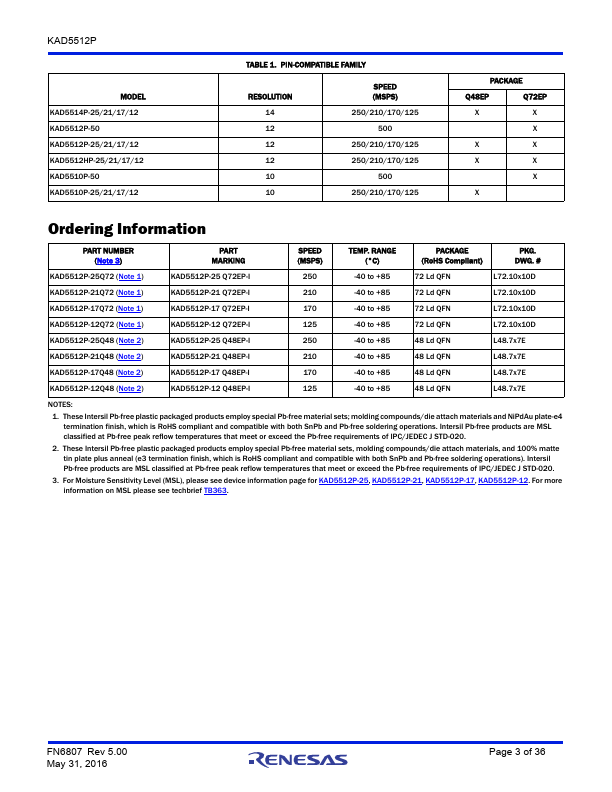

KAD5512P Low Power 12-Bit, 250/210/170/125MSPS ADC The KAD5512P is the low-power member of the KAD5512 family of 12-bit analog-to-digital converters. Designed with Intersil’s proprietary FemtoCharge™ technology on a standard CMOS process, the family supports sampling rates of up to 250MSPS. The KAD5512P is part of a pin-patible portfolio of 10, 12 and 14-bit A/Ds with sample rates ranging from 125MSPS to 500MSPS.

KAD5512P Key Features

- Half the power of the pin-patible KAD5512HP family

- 1.5GHz analog input bandwidth

- 60fs clock jitter

- Programmable gain, offset and skew control

- Over-range indicator

- Selectable clock divider: ÷1, ÷2 or ÷4

- Clock phase selection

- Nap and sleep modes

- Two’s plement, gray code or binary data format

- SDR/DDR LVDS-patible or LVCMOS outputs