TH58NVG7T2ELA46 Description

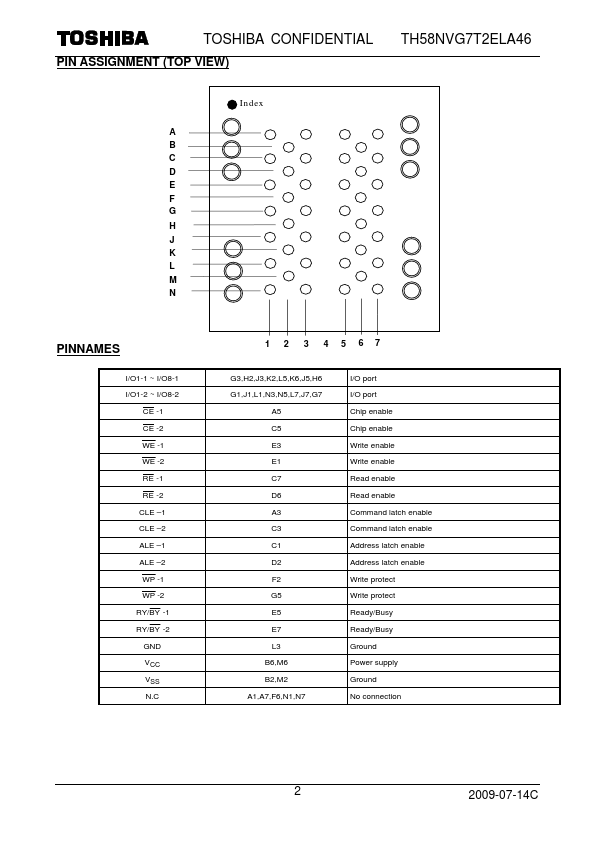

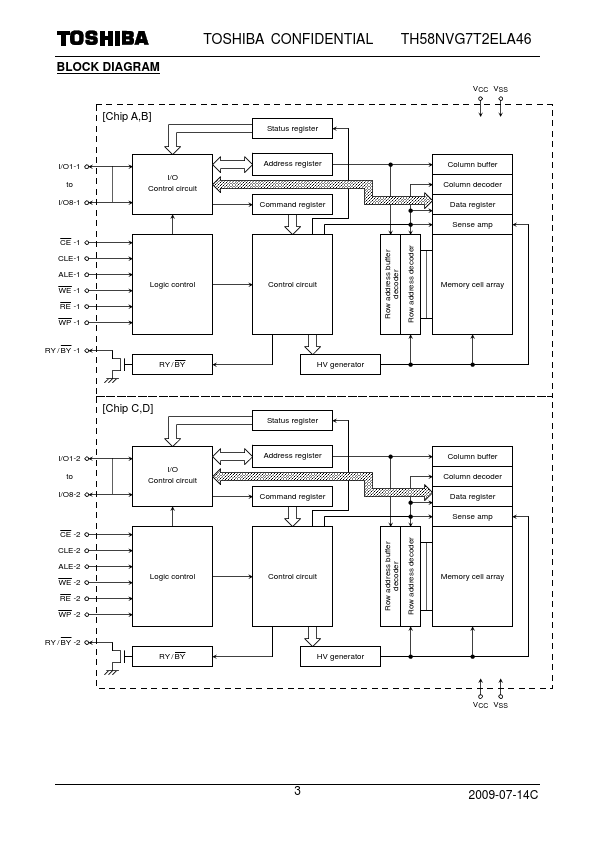

The device has two 8568-byte static registers which allow program and read data to be transferred between the register and the memory cell array in 8568-byte increments. The Erase operation is implemented in a single block unit (1536 Kbytes + 70.5 Kbytes:8568 bytes x 192 pages). The TH58NVG7T2E is a serial-type memory device which utilizes the I/O pins for both address and data input/output as well as for mand...

TH58NVG7T2ELA46 Key Features

- Organization

- Modes Read, Reset, Auto Page Program, Auto Block Erase, Status Read, Page Copy, Multi Page Program, Multi Block Erase,Mu

- Mode control Serial input/output

- Number of valid blocks Min 10624 blocks Max 11120 blocks

- Power supply VCC = 2.7 V to 3.6 V VCCQ = 2.7 V to 3.6 V

- Access time

- Program/Erase time Auto Page Program Auto Block Erase

- Operating current Read (25 ns cycle) Program (avg.)

- Package P

- TLGA40