TC55VZM216AFTN10

Overview

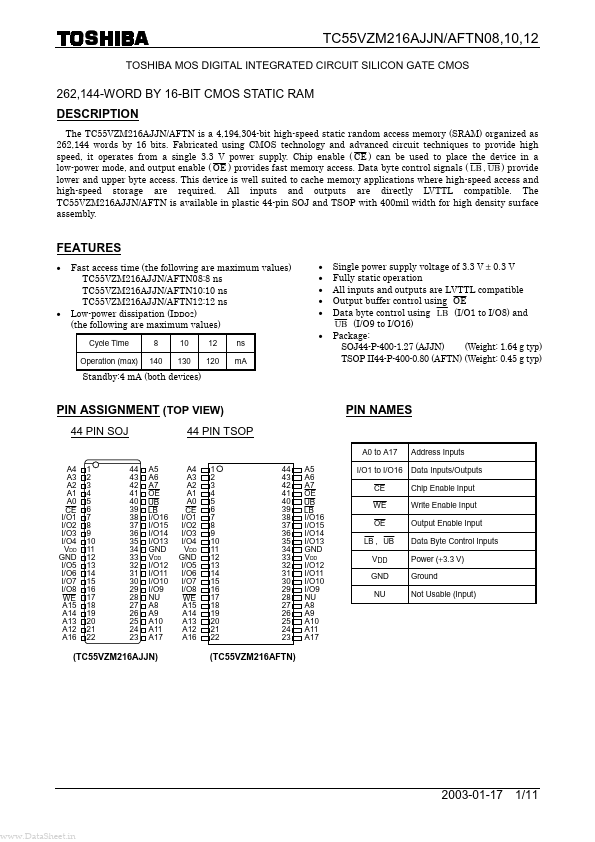

- Fast access time (the following are maximum values) TC55VZM216AJJN/AFTN08:8 ns TC55VZM216AJJN/AFTN10:10 ns TC55VZM216AJJN/AFTN12:12 ns Low-power dissipation (IDDO2) (the following are maximum values) Cycle Time Operation (max) 8 140 10 130 12 120 ns mA * * * * * *

- Single power supply voltage of 3.3 V ± 0.3 V Fully static operation All inputs and outputs are LVTTL compatible Output buffer control using OE Data byte control using LB (I/O1 to I/O8) and UB (I/O9 to I/O16) Package: SOJ44-P-400-1.27 (AJJN) (Weight: 1.64 g typ) TSOP II44-P-400-0.80 (AFTN) (Weight: 0.45 g typ) Standby:4 mA (both devices)