U74LVC1G74

U74LVC1G74 is SINGLE POSITIVE-EDGE-TRIGGERED D-TYPE FLIP-FLOP manufactured by Unisonic Technologies.

UNISONIC TECHNOLOGIES CO., LTD

SINGLE

POSITIVE-EDGE-TRIGGERED

D-TYPE FLIP-FLOP WITH

CLEAR AND PRESET

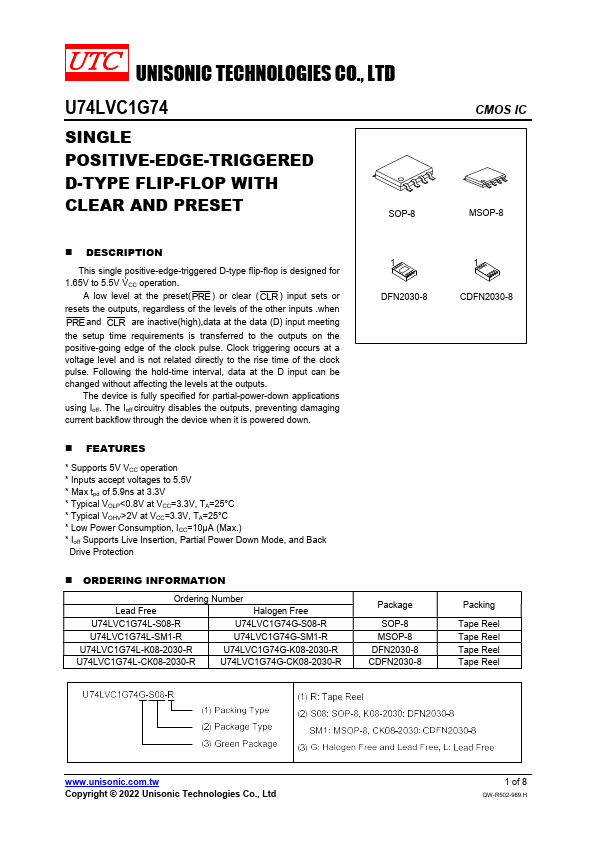

SOP-8

CMOS IC

MSOP-8

- DESCRIPTION

This single positive-edge-triggered D-type flip-flop is designed for 1.65V to 5.5V VCC operation.

A low level at the preset(PRE ) or clear ( CLR ) input sets or resets the outputs, regardless of the levels of the other inputs .when PRE and CLR are inactive(high),data at the data (D) input meeting the setup time requirements is transferred to the outputs on the positive-going edge of the clock pulse. Clock triggering occurs at a voltage level and is not related directly to the rise time of the clock pulse. Following the hold-time...