Datasheet Summary

Product Folder

Sample & Buy

Technical Documents

Tools & Software

Support & munity

SCAS898B

- MAY 2010

- REVISED OCTOBER 2016

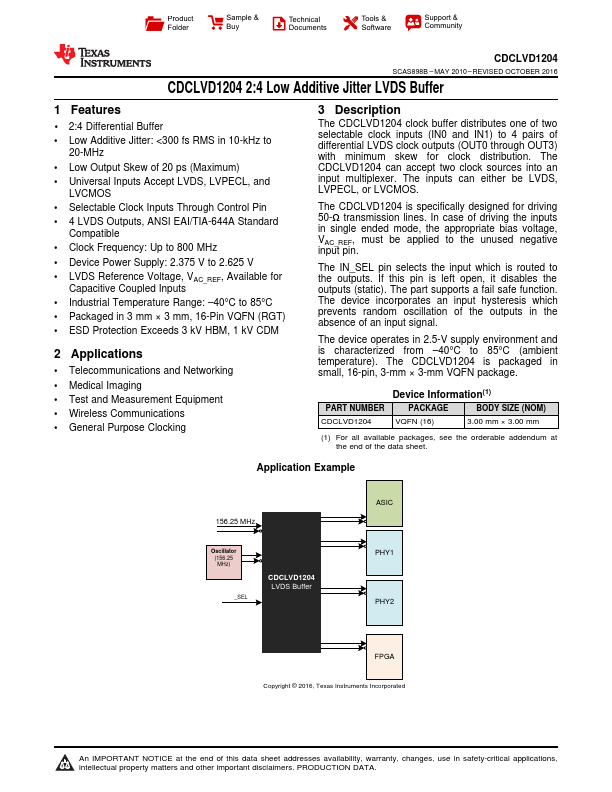

CDCLVD1204 2:4 Low Additive Jitter LVDS Buffer

1 Features

- 1 2:4 Differential Buffer

- Low Additive Jitter: <300 fs RMS in 10-kHz to

20-MHz

- Low Output Skew of 20 ps (Maximum)

- Universal Inputs Accept LVDS, LVPECL, and

LVCMOS

- Selectable Clock Inputs Through Control Pin

- 4 LVDS Outputs, ANSI EAI/TIA-644A Standard patible

- Clock Frequency: Up to 800 MHz

- Device Power Supply: 2.375 V to 2.625 V

- LVDS Reference Voltage, VAC_REF, Available for

Capacitive Coupled Inputs

- Industrial Temperature Range:

- 40°C to 85°C

- Packaged in 3 mm × 3 mm,...