Datasheet Summary

.ti.

SCAS933

- DECEMBER 2012

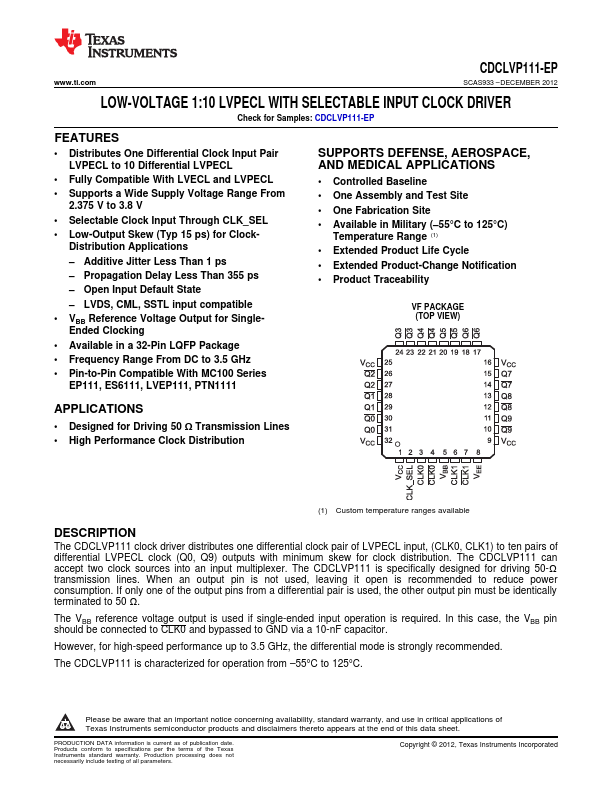

LOW-VOLTAGE 1:10 LVPECL WITH SELECTABLE INPUT CLOCK DRIVER

Check for Samples: CDCLVP111-EP

Features

- Distributes One Differential Clock Input Pair LVPECL to 10 Differential LVPECL

- Fully patible With LVECL and LVPECL

- Supports a Wide Supply Voltage Range From

2.375 V to 3.8 V

- Selectable Clock Input Through CLK_SEL

- Low-Output Skew (Typ 15 ps) for Clock-

Distribution Applications

- Additive Jitter Less Than 1 ps

- Propagation Delay Less Than 355 ps

- Open Input Default State

- LVDS, CML, SSTL input patible

- VBB Reference Voltage Output for SingleEnded Clocking

- Available in a 32-Pin LQFP Package

- Frequency Range From DC to...