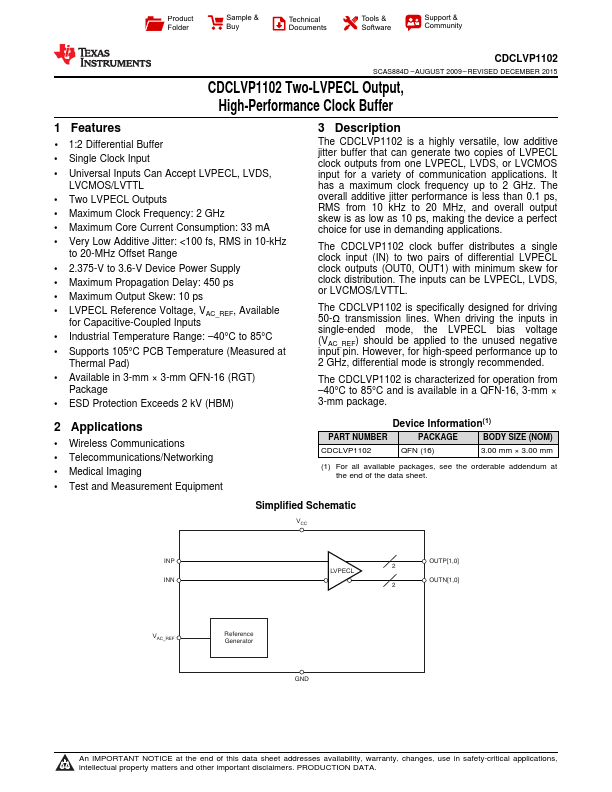

CDCLVP1102 Description

The CDCLVP1102 is a highly versatile, low additive jitter buffer that can generate two copies of LVPECL clock outputs from one LVPECL, LVDS, or LVCMOS input for a variety of munication applications. It has a maximum clock frequency up to 2 GHz. The overall additive jitter performance is less than 0.1 ps, RMS from 10 kHz to 20 MHz, and overall output skew is as low as 10 ps, making the device a perfect choice for use...

CDCLVP1102 Key Features

- 1 1:2 Differential Buffer

- Single Clock Input

- Universal Inputs Can Accept LVPECL, LVDS

- Two LVPECL Outputs

- Maximum Clock Frequency: 2 GHz

- Maximum Core Current Consumption: 33 mA

- Very Low Additive Jitter: <100 fs, RMS in 10-kHz

- 2.375-V to 3.6-V Device Power Supply

- Maximum Propagation Delay: 450 ps

- Maximum Output Skew: 10 ps