Datasheet Summary

.ti.

SCAS727F

- NOVEMBER 2003

- REVISED DECEMBER 2013

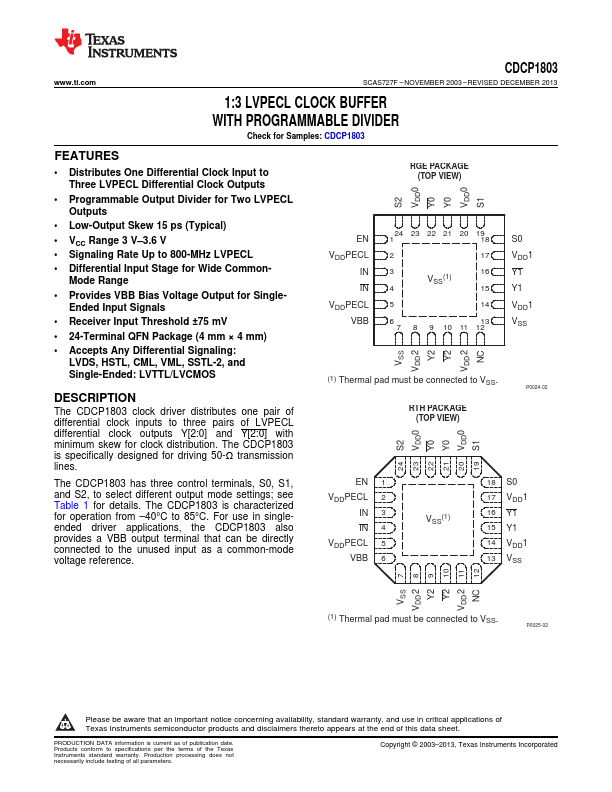

1:3 LVPECL CLOCK BUFFER WITH PROGRAMMABLE DIVIDER

Check for Samples: CDCP1803

Features

- Distributes One Differential Clock Input to Three LVPECL Differential Clock Outputs

- Programmable Output Divider for Two LVPECL Outputs

- Low-Output Skew 15 ps (Typical)

- VCC Range 3 V- 3.6 V

- Signaling Rate Up to 800-MHz LVPECL

- Differential Input Stage for Wide monMode Range

- Provides VBB Bias Voltage Output for SingleEnded Input Signals

- Receiver Input Threshold ±75 mV

- 24-Terminal QFN Package (4 mm × 4 mm)

- Accepts Any Differential Signaling: LVDS, HSTL, CML, VML, SSTL-2, and Single-Ended: LVTTL/LVCMOS

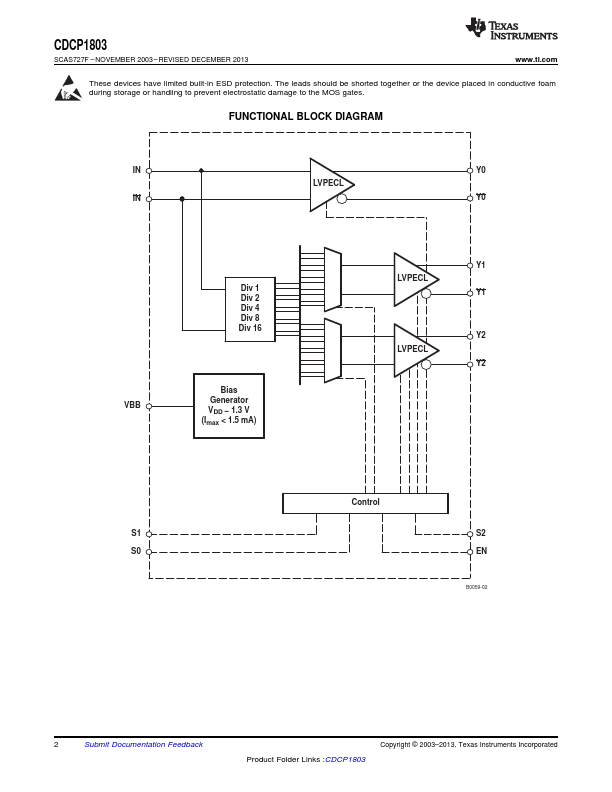

DESCRIPTION

The...