Datasheet Summary

Product Folder

Sample & Buy

Technical Documents

Tools & Software

Support & munity

SCAS640G

- JULY 2000

- REVISED AUGUST 2016

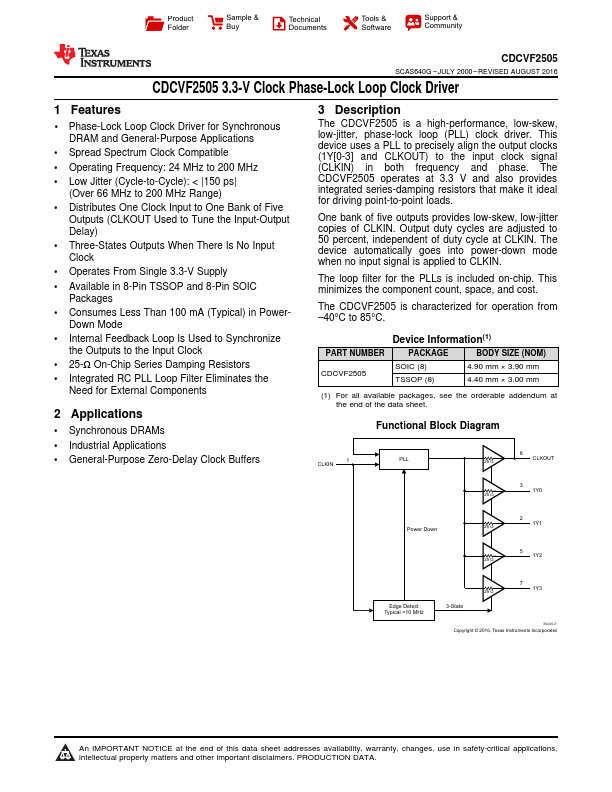

CDCVF2505 3.3-V Clock Phase-Lock Loop Clock Driver

1 Features

- 1 Phase-Lock Loop Clock Driver for Synchronous DRAM and General-Purpose Applications

- Spread Spectrum Clock patible

- Operating Frequency: 24 MHz to 200 MHz

- Low Jitter (Cycle-to-Cycle): < |150 ps|

(Over 66 MHz to 200 MHz Range)

- Distributes One Clock Input to One Bank of Five

Outputs (CLKOUT Used to Tune the Input-Output Delay)

- Three-States Outputs When There Is No Input Clock

- Operates From Single 3.3-V Supply

- Available in 8-Pin TSSOP and 8-Pin SOIC Packages

- Consumes Less...