Datasheet Summary

SCAS671B

- OCTOBER 2001

- REVISED JANUARY 2022

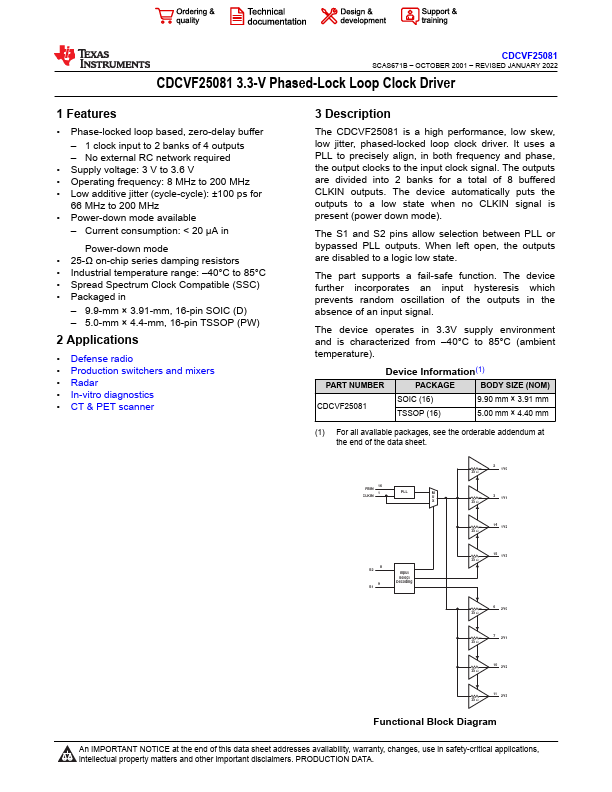

CDCVF25081 3.3-V Phased-Lock Loop Clock Driver

1 Features

- Phase-locked loop based, zero-delay buffer

- 1 clock input to 2 banks of 4 outputs

- No external RC network required

- Supply voltage: 3 V to 3.6 V

- Operating frequency: 8 MHz to 200 MHz

- Low additive jitter (cycle-cycle): ±100 ps for

66 MHz to 200 MHz

- Power-down mode available

- Current consumption: < 20 µA in

Power-down mode

- 25-Ω on-chip series damping resistors

- Industrial temperature range:

- 40°C to 85°C

- Spread Spectrum Clock patible (SSC)

- Packaged in

- 9.9-mm × 3.91-mm, 16-pin SOIC (D)

- 5.0-mm × 4.4-mm, 16-pin TSSOP (PW)

2 Applications

- Defense radio

-...