Datasheet Summary

.ti. ............................................................................................................................................... SCAS764C

- MARCH 2004

- REVISED FEBRUARY 2009

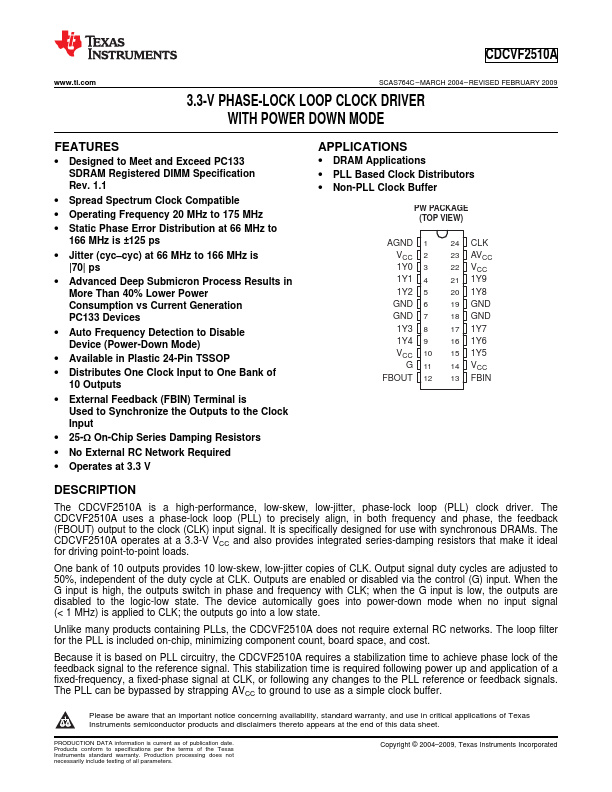

3.3-V PHASE-LOCK LOOP CLOCK DRIVER WITH POWER DOWN MODE

Features

- Designed to Meet and Exceed PC133 SDRAM Registered DIMM Specification Rev. 1.1

- Spread Spectrum Clock patible

- Operating Frequency 20 MHz to 175 MHz

- Static Phase Error Distribution at 66 MHz to

166 MHz is ±125 ps

- Jitter (cyc- cyc) at 66 MHz to 166 MHz is |70| ps

- Advanced Deep Submicron Process Results in More Than 40% Lower Power Consumption vs Current Generation PC133 Devices

- Auto Frequency...