CDCVF2510 Description

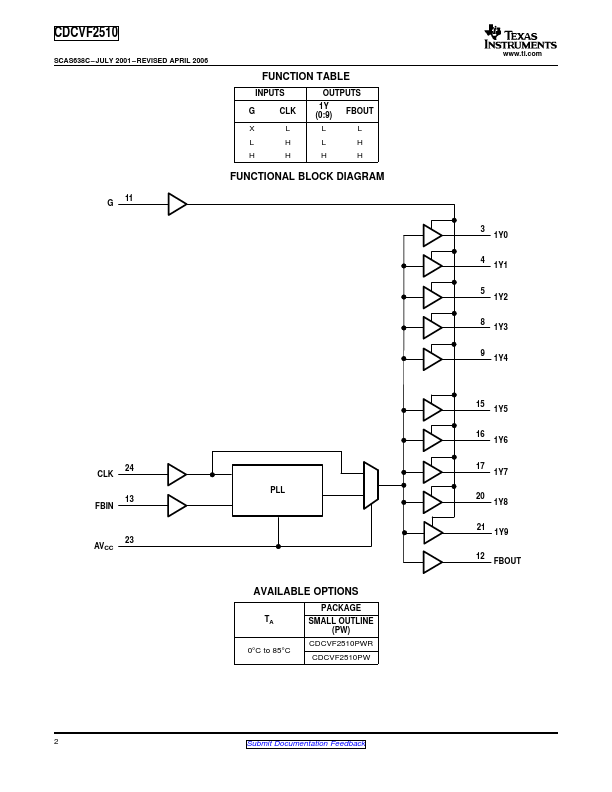

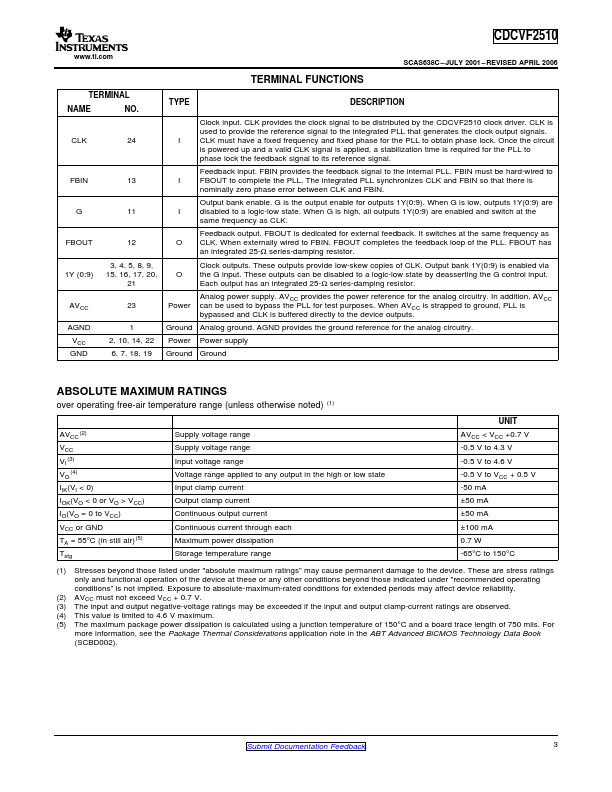

The CDCVF2510 is a high-performance, low-skew, low-jitter, phase-lock loop (PLL) clock driver. It uses a phase-lock loop (PLL) to precisely align, in both frequency and phase, the feedback (FBOUT) output to the clock (CLK) input signal. It is specifically designed for use with synchronous DRAMs.

CDCVF2510 Key Features

- Designed to Meet and Exceed PC133 SDRAM Registered DIMM Specification Rev. 1.1

- Spread Spectrum Clock patible

- Operating Frequency 50 MHz to 175 MHz

- Jitter (cyc

- cyc) at 66 MHz to 166 MHz Is |70| ps

- Advanced Deep Submicron Process Results in More Than 40% Lower Power Consumption Versus Current Generation PC133 Devices

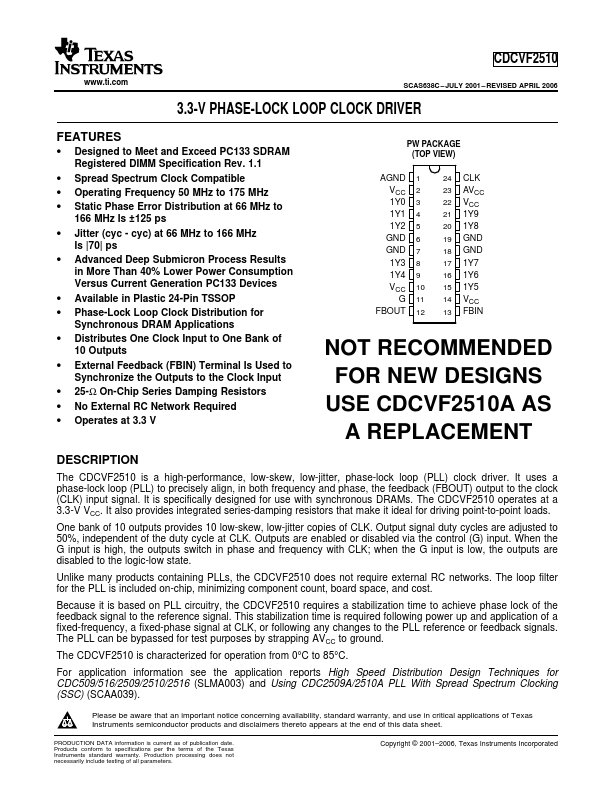

- Available in Plastic 24-Pin TSSOP

CDCVF2510 Applications

- Distributes One Clock Input to One Bank of 10 Outputs

- External Feedback (FBIN) Terminal Is Used to Synchronize the Outputs to the Clock Input