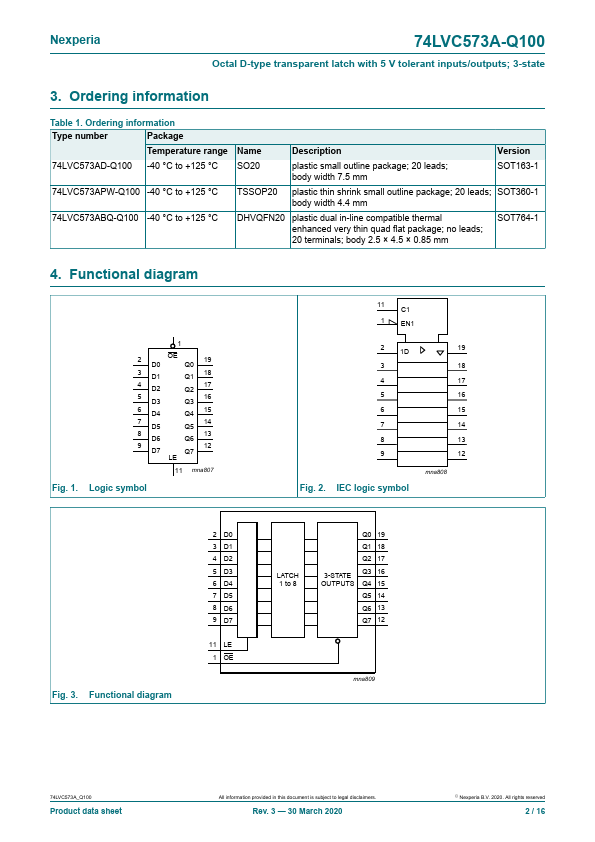

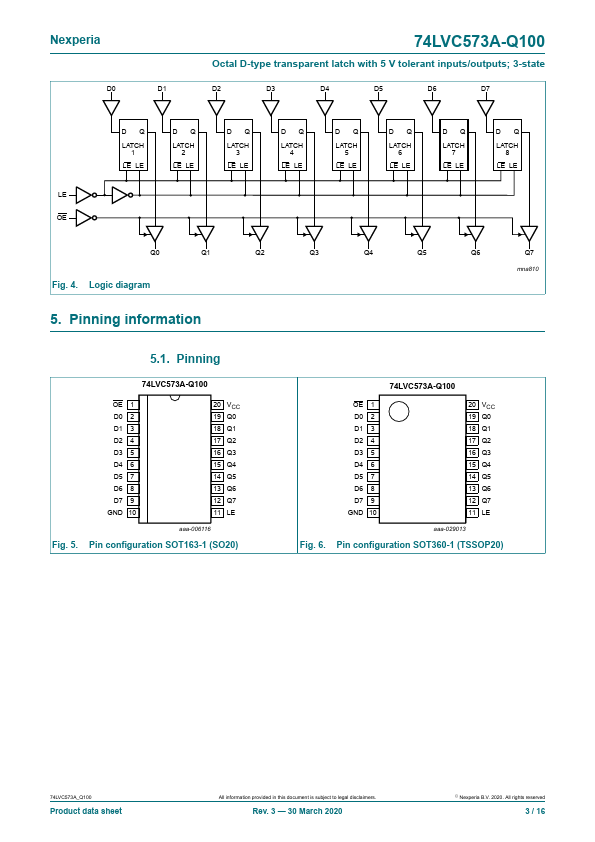

74LVC573A-Q100 Description

The 74LVC573A-Q100 consists of eight D-type transparent latches, featuring separate D-type inputs for each latch and 3-state true outputs for bus-oriented applications. A Latch Enable (LE) input and an Output Enable (OE) input are mon to all internal latches. When LE is HIGH, data at the Dn inputs enters the latches.

74LVC573A-Q100 Applications

- Automotive product qualification in accordance with AEC-Q100 (Grade 1)

- Specified from -40 °C to +85 °C and from -40 °C to +125 °C

- 5 V tolerant inputs/outputs, for interfacing with 5 V logic

- Supply voltage range from 1.2 V to 3.6 V