Description

3

ARM Cortex-A55 Processor 5 SHARC Processor 6 SHARC+ Core Architecture 8 System Infrastructure 10 System Memory Map 11 Security

Features

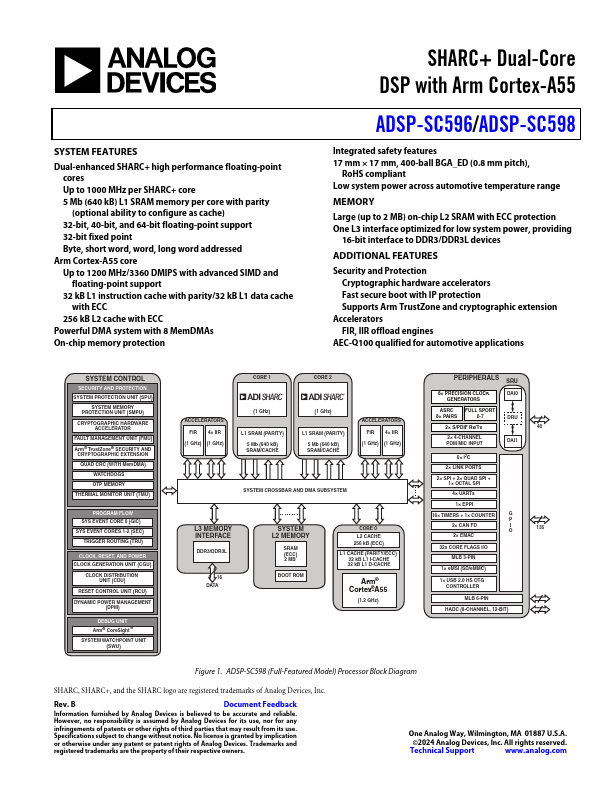

- Dual-enhanced SHARC+ high performance floating-point cores Up to 1000 MHz per SHARC+ core 5 Mb (640 kB) L1 SRAM memory per core with parity (optional ability to configure as cache) 32-bit, 40-bit, and 64-bit floating-point support 32-bit fixed point Byte, short word, word, long word addressed

Arm Cortex-A55 core Up to 1200 MHz/3360 DMIPS with advanced SIMD and floating-point support 32 kB L1 instruction cache with parity/32 kB L1 data cache with ECC 256 kB L2 cache with ECC

Powerful DMA system w.