Datasheet Details

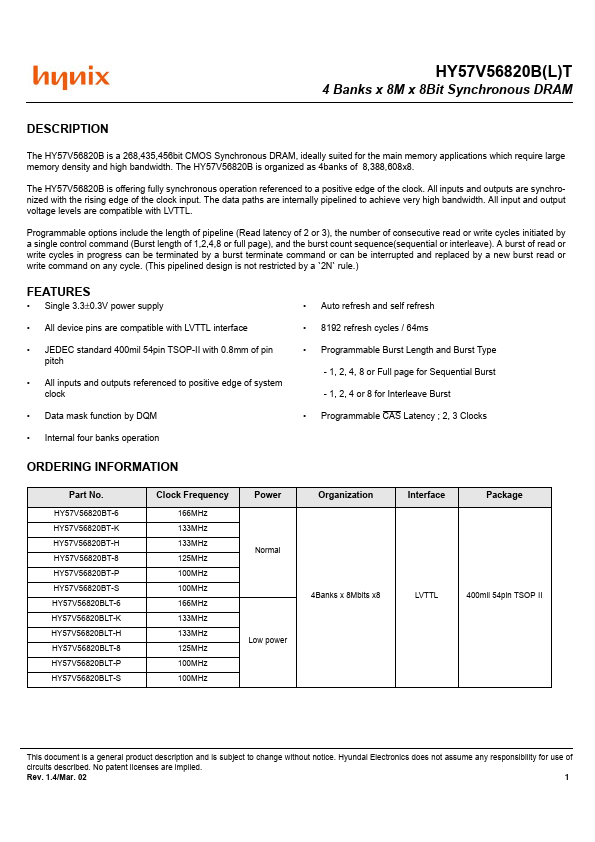

| Part number | HY57V56820BLT, HY57V56820BT |

|---|---|

| Manufacturer | Hynix Semiconductor |

| File Size | 173.15 KB |

| Description | 4 Banks x 8M x 8Bit Synchronous DRAM |

| Datasheet |

|

| Note |

This datasheet PDF includes multiple part numbers: HY57V56820BLT, HY57V56820BT. Please refer to the document for exact specifications by model. |