Description

AUGUST 2017

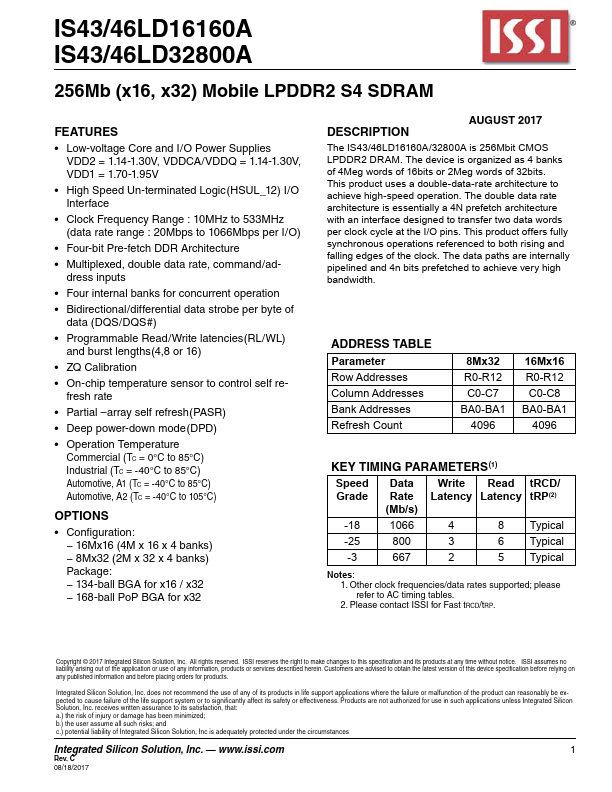

The IS43/46LD16160A/32800A is 256Mbit CMOS LPDDR2 DRAM.The device is organized as 4 banks of 4Meg words of 16bits or 2Meg words of 32bits.This product uses a double-data-rate architecture to achieve high-speed operation.The double data rate architecture is essentially a 4N prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins.This product offers fully synchronous operations referenced to both rising and falling edges of the

Features

- Low-voltage Core and I/O Power Supplies VDD2 = 1.14-1.30V, VDDCA/VDDQ = 1.14-1.30V, VDD1 = 1.70-1.95V.

- High Speed Un-terminated Logic(HSUL_12) I/O Interface.

- Clock Frequency Range : 10MHz to 533MHz (data rate range : 20Mbps to 1066Mbps per I/O).

- Four-bit Pre-fetch DDR Architecture.

- Multiplexed, double data rate, command/address inputs.

- Four internal banks for concurrent operation.

- Bidirectional/differential data strobe per byte of d.