Description

x8

A0-A12 A0-A9 BA0, BA1 DQ0

DQ7 CK, CK CKE CS CAS RAS WE Row Address Input Column Address Input Bank Select Address Data I/O System Clock Input Clock Enable Chip Select Column Address Strobe Command Row Address Strobe Command Write Enable DM DQS VDD VDDQ VSS VSSQ VREF NC Data Write Mask Data Strobe Power Power Supply for I/O Pins Ground Ground for I/O Pins SSTL_2 reference voltage No Connection

4

Integrated Silicon Solution, Inc.Rev. B 06/19/2012

Datasheet pdf - http://www.Dat

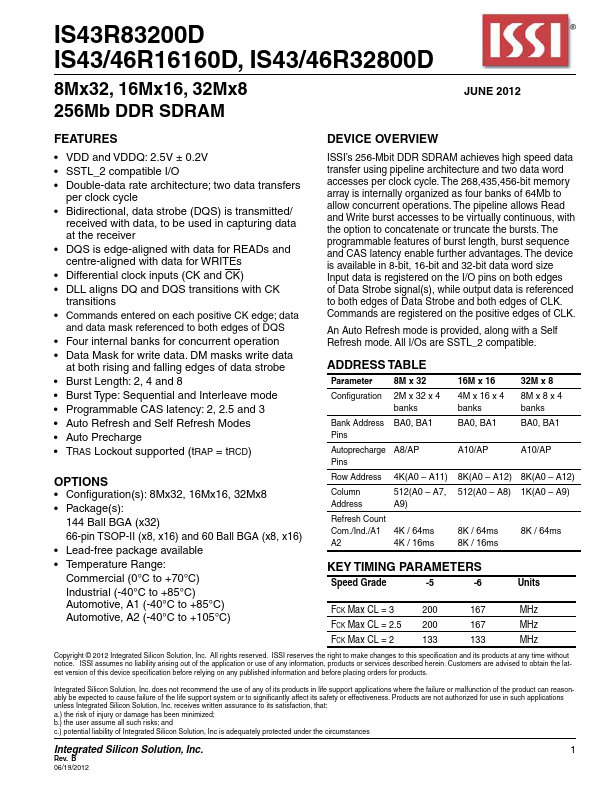

Features

- VDD and VDDQ: 2.5V ± 0.2V.

- SSTL_2 compatible I/O.

- Double-data rate architecture; two data transfers per clock cycle.

- Bidirectional, data strobe (DQS) is transmitted/ received with data, to be used in capturing data at the receiver.

- DQS is edge-aligned with data for READs and centre-aligned with data for WRITEs.

- Differential clock inputs (CK and CK).

- DLL aligns DQ and DQS transitions with CK transitions.

- Commands ent.