MK2049-45

Description

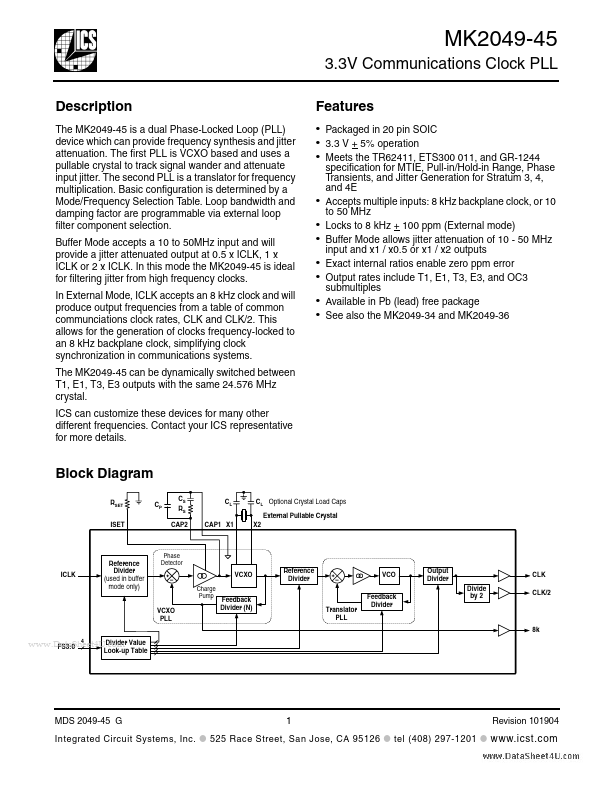

The MK2049-45 is a dual Phase-Locked Loop (PLL) device which can provide frequency synthesis and jitter attenuation. The first PLL is VCXO based and uses a pullable crystal to track signal wander and attenuate input jitter.

Key Features

- Packaged in 20 pin SOIC

- 3.3 V + 5% operation