Description

General Description

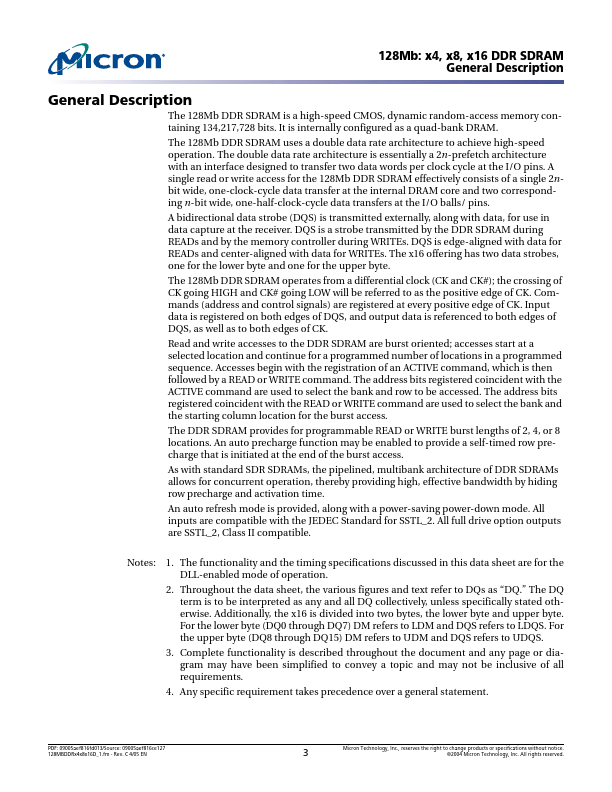

The 128Mb DDR SDRAM is a high-speed CMOS, dynamic random-access memory containing 134,217,728 bits.It is internally configured as a quad-bank DRAM.The 128Mb DDR SDRAM uses a double data rate architecture to achieve high-speed operation.The double data rate architecture is essentially a 2n-prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins.A single read or write access for the 128Mb DDR SDRAM effectively consists of

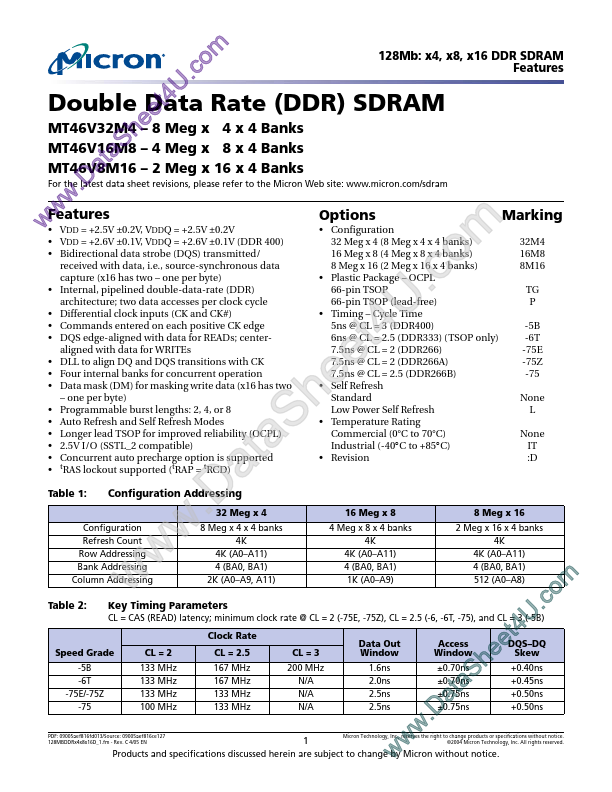

Features

- c . U 4 t Double Data Rate (DDR) SDRAM e e8 Meg x 4 x 4 Banks MT46V32M4h.

- S.

- 4 Meg x 8 x 4 Banks MT46V16M8 a MT46V8M16 at.

- 2 Meg x 16 x 4 Banks . D w w Features Options Marking w

For the latest data sheet revisions, please refer to the Micron Web site: www. micron. com/sdram.

- VDD = +2.5V ±0.2V, VDDQ = +2.5V ±0.2V.

- VDD = +2.6V ±0.1V, VDDQ = +2.6V ±0.1V (DDR 400).

- Bidirectional data strobe (DQS) transmitted/ received with data, i. e. , source-synch.