Description

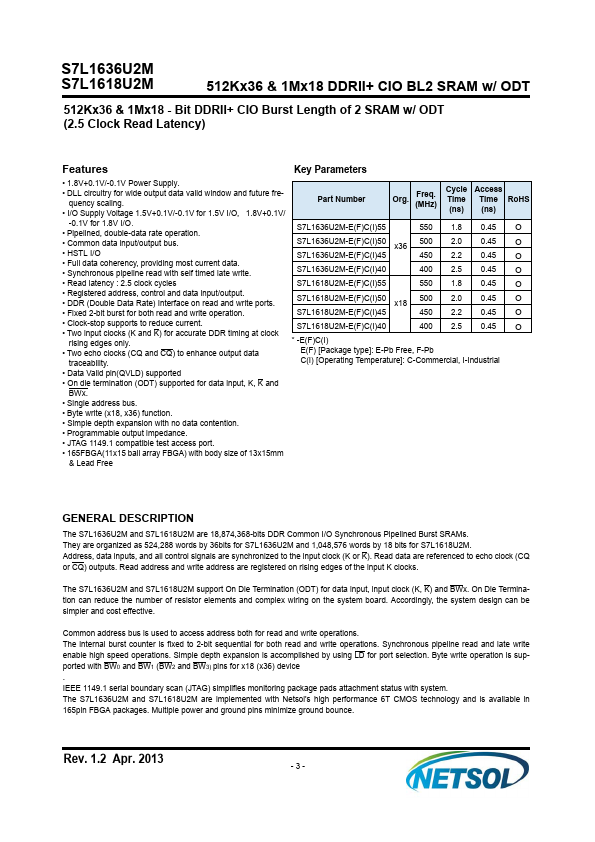

The S7L1636U2M and S7L1618U2M are 18,874,368-bits DDR Common I/O Synchronous Pipelined Burst SRAMs.

Features

- Key Parameters.

- 1.8V+0.1V/-0.1V Power Supply.

- DLL circuitry for wide output data valid window and future fre-

quency scaling.

- I/O Supply Voltage 1.5V+0.1V/-0.1V for 1.5V I/O, 1.8V+0.1V/

Part Number

Org. Freq. (MHz)

Cycle Access Time Time RoHS (ns) (ns)

-0.1V for 1.8V I/O.

- Pipelined, double-data rate operation.

- Common data input/output bus.

- HSTL I/O.

- Full data coherency, providing most current data.

- Synchronous p.

S7L1636U2M-NETSOL.pdf

S7L1636U2M-NETSOL.pdf