Description

Input Clock Q Valid output Output Echo Clock DLL Disable Address Inputs Data Inputs Outputs Read, Write Control Pin, Read active when high Synchronous Load Pin, bus Cycle sequence is to be defined when low Block Write Control Pin,active when low Input Reference Voltage Output Driver Impedance Control Input Power Supply ( 1.8 V ) Output Power Supply ( 1.5 ) Ground JTAG Test Mode Select JTAG Test Data Input JTAG Test Clock JTAG Test Data Output No Connect 2 1 NOTE

R/W LD BW0, BW1,BW2, BW3 VREF ZQ

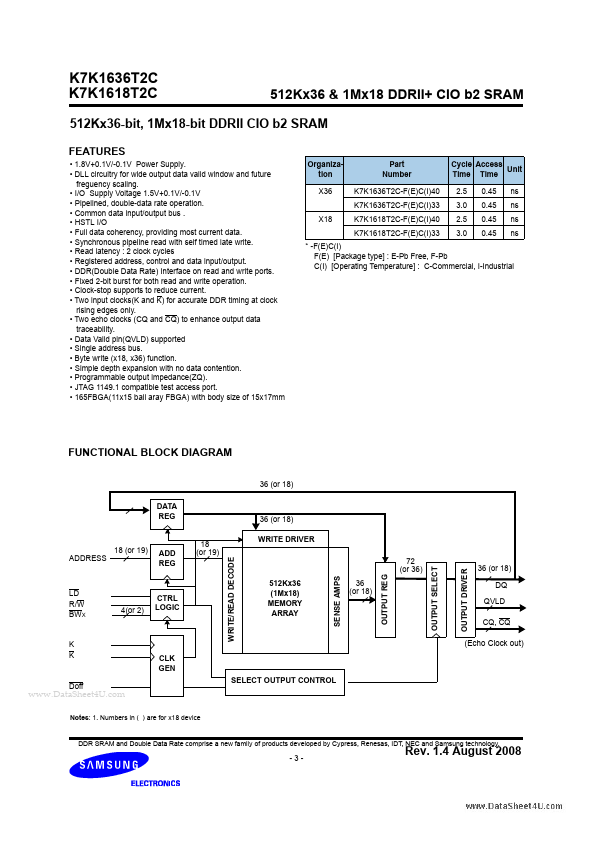

Features

- 1.8V+0.1V/-0.1V Power Supply.

- DLL circuitry for wide output data valid window and future freguency scaling.

- I/O Supply Voltage 1.5V+0.1V/-0.1V.

- Pipelined, double-data rate operation.

- Common data input/output bus.

- HSTL I/O.

- Full data coherency, providing most current data.

- Synchronous pipeline read with self timed late write.

- Read latency : 2 clock cycles.

- Registered address, control and data input/o.