74HC74AP

Features

- -

- -

- -

- - High speed: fmax = 77 MHz (typ.) at VCC = 5 V Low power dissipation: ICC = 2 μA (max) at Ta = 25°C High noise immunity: VNIH = VNIL = 28% VCC (min) Output drive capability: 10 LSTTL loads Symmetrical output impedance: |IOH| = IOL = 4 m A (min) ∼ tp HL Balanced propagation delays: tp LH

- Wide operating voltage range: VCC (opr) = 2~6 V Pin and function patible with 74LS74

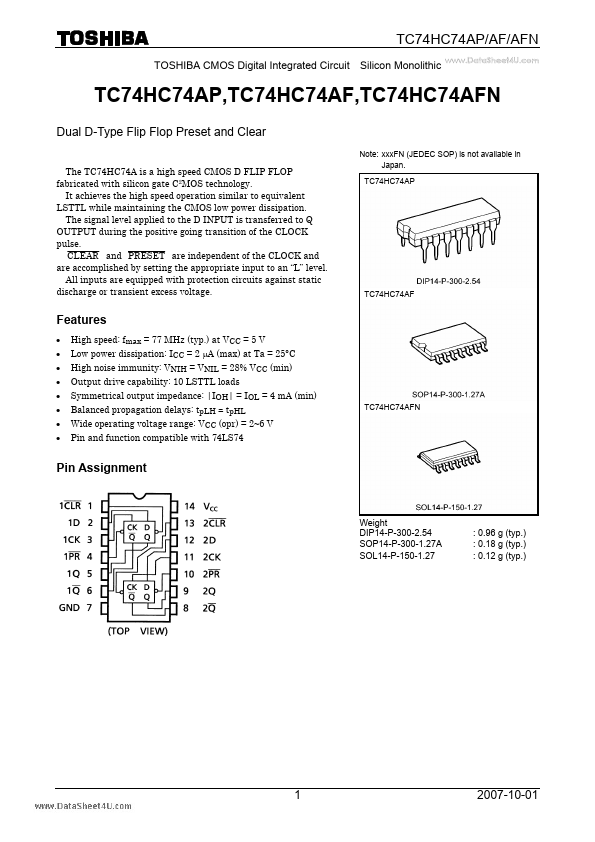

TC74HC74AFN

Pin Assignment

Weight DIP14-P-300-2.54 SOP14-P-300-1.27A SOL14-P-150-1.27

: 0.96 g (typ.) : 0.18 g (typ.) : 0.12 g (typ.)

2007-10-01

TC74HC74AP/AF/AFN

IEC Logic Symbol

..

Truth Table

Inputs

Outputs

PR H L L H H H

D X X X L H X

CK X X X

Q L H H L H Qn

Function Clear Preset

⎯ ⎯ ⎯

L H L H H H

H L H H L

Qn

No Change

X: Don’t care

System Diagram

2007-10-01

TC74HC74AP/AF/AFN

Absolute Maximum Ratings (Note 1)

Characteristics Supply voltage range DC input voltage DC output voltage Input diode current Output diode current DC output current DC VCC/ground current...