MT5C6404 Overview

Key Specifications

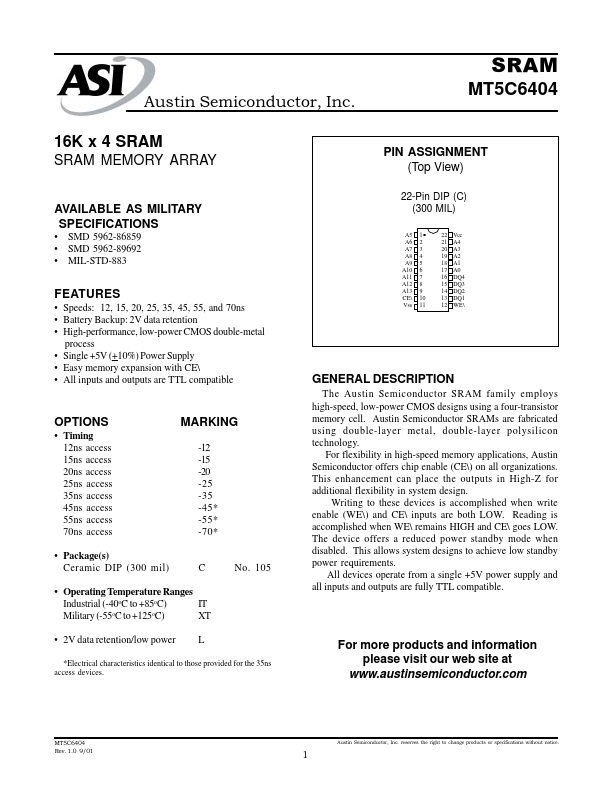

Package: DIP

Operating Voltage: 5 V

Max Voltage (typical range): 5.5 V

Min Voltage (typical range): 4.5 V

Description

The Austin Semiconductor SRAM family employs high-speed, low-power CMOS designs using a four-transistor memory cell. Austin Semiconductor SRAMs are fabricated using double-layer metal, double-layer polysilicon technology.

Key Features

- Battery Backup: 2V data retention

- High-performance, low-power CMOS double-metal process

- Single +5V (+10%) Power Supply

- Easy memory expansion with CE\

- All inputs and outputs are TTL compatible