Datasheet Summary

Standard Products

UT8SF2M32 64Megabit Flow-thru SSRAM

Preliminary Datasheet .aeroflex./memories April 2015

Features

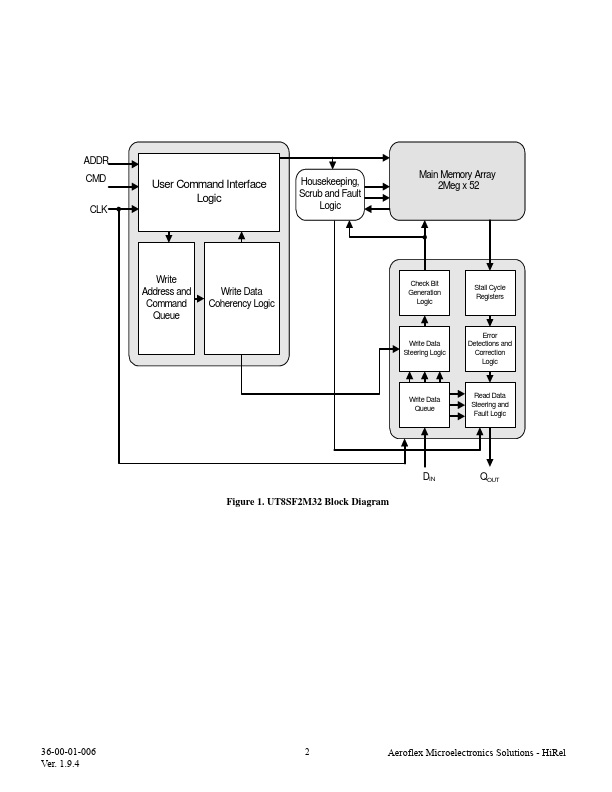

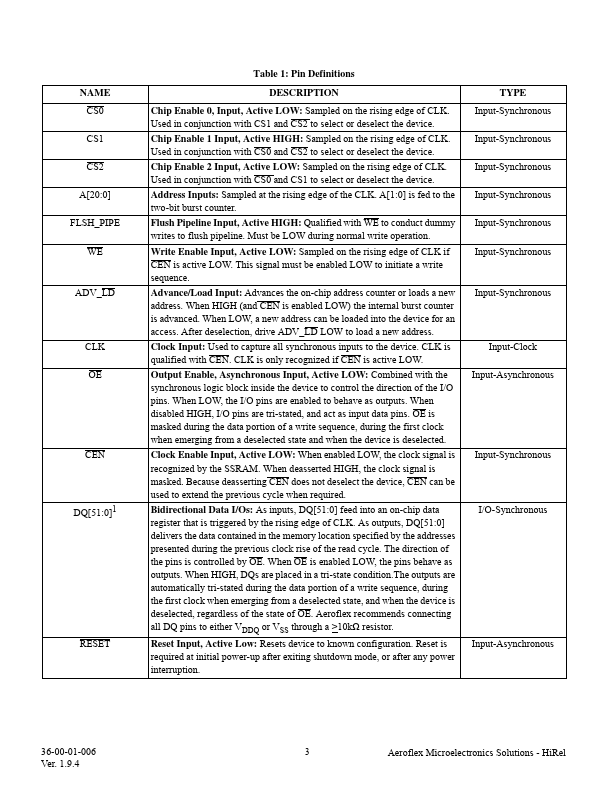

Synchronous SRAM organized as 2Meg words x 32bit Continuous Data Transfer (CDT) architecture eliminates wait states between read and write operations Supports 40MHz to 80MHz bus operations Internally self-timed output buffer control eliminates the need for synchronous output enable Registered inputs for flow-thru operations Single 2.5V to 3.3V supply Clock-to-output times

- Clk to Q = 12ns Clock Enable (CEN) pin to enable clock and suspend operation Synchronous self-timed writes Three Chip Enables (CS0, CS1, CS2) for simple depth expansion "ZZ"...