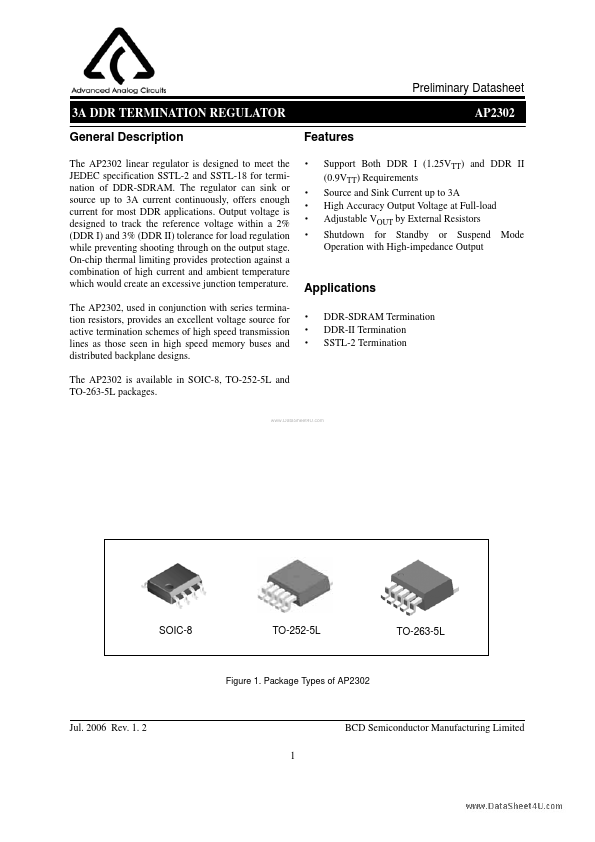

AP2302 Overview

Key Features

- Support Both DDR I (1.25VTT) and DDR II (0.9VTT) Requirements Source and Sink Current up to 3A High Accuracy Output Voltage at Full-load Adjustable VOUT by External Resistors Shutdown for Standby or Suspend Operation with High-impedance Output Mode

- DDR-SDRAM Termination DDR-II Termination SSTL-2 Termination