CY2303

Overview

- 3-Multiplier configuration (1x, 2x, 4x ref)

- 10 MHz to 166.67 MHz operating range (reference input from 10 MHz to 41.67 MHz)

- Phase alignment

- 80 ps typical period jitter

- Output enable pin

- 3.3 V operation

- 5 V tolerant input

- 8-pin 150-mil small-outline integrated circuit (SOIC) package

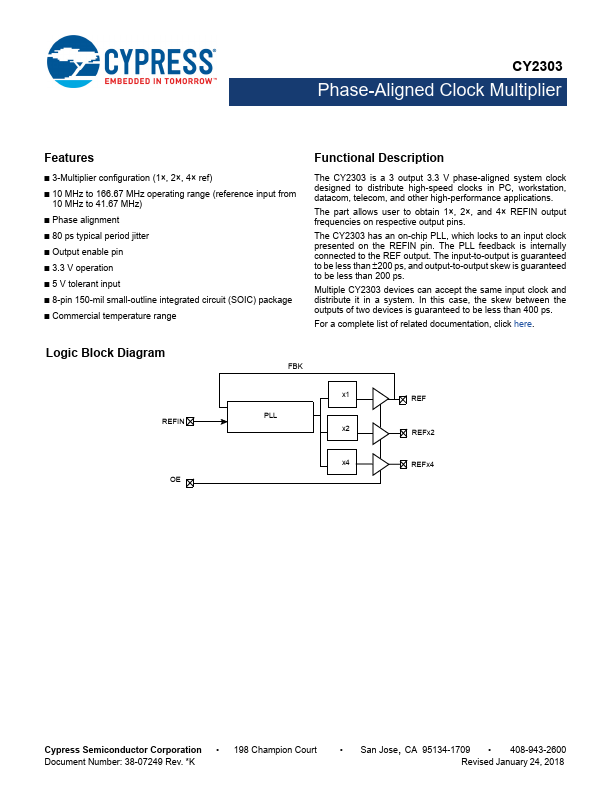

- Commercial temperature range Functional Description The CY2303 is a 3 output 3.3 V phase-aligned system clock designed to distribute high-speed clocks in PC, workstation, datacom, telecom, and other high-performance applications. The part allows user to obtain 1x, 2x, and 4x REFIN output frequencies on respective output pins. The CY2303 has an on-chip PLL, which locks to an input clock presented on the REFIN pin. The PLL feedback is internally connected to the REF output. The input-to-output is guaranteed to be less than 200 ps, and output-to-output skew is guaranteed to be less than 200 ps.