Datasheet Summary

USE ULTRA37000™ FOR ALL NEW DESIGNS

UltraLogic™ 32-Macrocell Flash CPLD

Features

- -

- -

- -

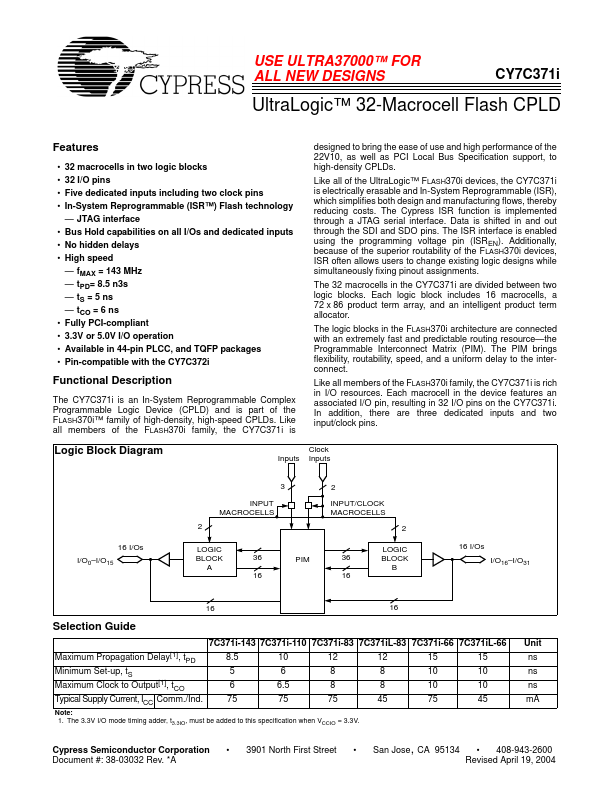

- 32 macrocells in two logic blocks 32 I/O pins Five dedicated inputs including two clock pins In-System Reprogrammable (ISR™) Flash technology

- JTAG interface Bus Hold capabilities on all I/Os and dedicated inputs No hidden delays High speed

- fMAX = 143 MHz

- tPD= 8.5 n3s

- tS = 5 ns

- tCO = 6 ns Fully PCI-pliant 3.3V or 5.0V I/O operation Available in 44-pin PLCC, and TQFP packages Pin-patible with the CY7C372i designed to bring the ease of use and high performance of the 22V10, as well as PCI Local Bus Specification support, to high-density CPLDs. Like all of the UltraLogic™...