CYRS1542AV18

CYRS1542AV18 is 72-Mbit QDR II+ SRAM Two-Word Burst Architecture manufactured by Cypress.

CYRS1544AV18

72-Mbit QDR® II+ SRAM Two-Word Burst Architecture with Rad Stop™ Technology

72-Mbit QDR® II+ SRAM Two-Word Burst Architecture with Rad Stop™ Technology

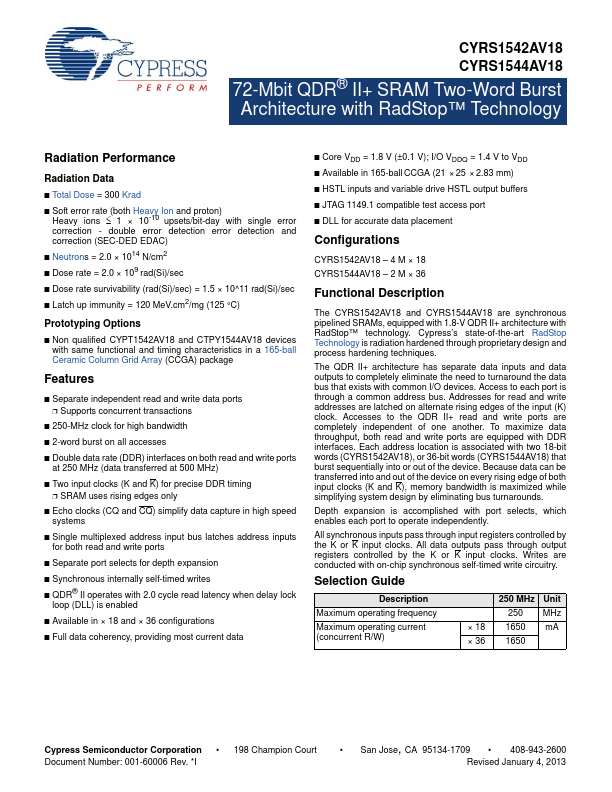

Radiation Performance

Radiation Data

- Total Dose =300 Krad

- Soft error rate (both Heavy Ion and proton) Heavy ions 1 × 10-10 upsets/bit-day with single error correction

- double error detection error detection and correction (SEC-DED EDAC)

- Neutrons = 2.0 × 1014 N/cm2

- Dose rate = 2.0 × 109 rad(Si)/sec

- Dose rate survivability (rad(Si)/sec) = 1.5 × 10^11 rad(Si)/sec

- Latch up immunity = 120 Me V.cm2/mg (125 °C)

Prototyping Options

- Non qualified CYPT1542AV18 and CTPY1544AV18 devices with same functional and timing characteristics in a 165-ball Ceramic Column Grid Array (CCGA) package

Features

- Separate independent read and write data ports

- Supports concurrent transactions

- 250-MHz clock for high bandwidth

- 2-word burst on all accesses

- Double data rate (DDR) interfaces on both read and write ports at 250 MHz (data transferred at 500 MHz)

- Two input clocks (K and K) for precise DDR timing

- SRAM uses rising edges only

- Echo clocks (CQ and CQ) simplify data capture in high speed systems

- Single multiplexed address input bus latches address inputs for both read and write ports

- Separate port selects for depth expansion

- Synchronous internally self-timed writes

- QDR® II operates with 2.0 cycle read latency when delay lock loop (DLL) is enabled

- Available in × 18 and × 36 configurations

- Full data coherency, providing most current data

- Core VDD = 1.8 V (±0.1 V); I/O VDDQ = 1.4 V to...